# VANGO TECHNOLOGIES, INC.

# V9160 Datasheet

#### Function

The V9160 is a three - phase metering chip. It supports full-wave and fundamental-wave energy metering in various modes, and can monitor a variety of power grid events. At the same time, the sampled data can be transmitted out via DMA according to the SPI protocol.

# Function

- Power Supply: 3.3V power supply, voltage input range 3.0 3.6V

- Reference Voltage: 1.2V (typical temperature coefficient 10 ppm/°C)

- Power Consumption:

Typical power consumption of the chip during normal operation at room temperature:

- 8.5 mA (when the system clock is 26.2144 MHz)

- Measurement Features:

- 6 independent oversampling  $\Sigma/\Delta$  ADCs: 3 voltage channels and 3 current channels

- Supports arbitrary mapping of voltage/ current channels, adjustable through configuration registers

- Measurement accuracy:

- Meets the requirements of IEC 62053-21:2020/ IEC 62053-22:2020 and IEC 62053-23:2020

- Within a 10000:1 dynamic range, the error of full-wave / fundamental active energy measurement is less than 0.1%

- Within a 10000:1 dynamic range, the error of full-wave/ fundamental reactive energy measurement is less than 0.1%

- Within a 2000:1 dynamic range, the error of full-wave/ fundamental voltage / current RMS value is less than 0.2%

- Measurement data:

- Instantaneous and average values of full-wave/ fundamental current/ voltage RMS Instantaneous and average values of full-wave/ fundamental active / reactive power Instantaneous and average values of full-wave apparent power

- Active/ reactive/ apparent power/ current RMS/ constant values

- Three-phase line voltage value

- Vector sum value of three-phase current

- Frequency and phase

- Supports software calibration

- Supports small signal accelerated calibration

- Supports Detection of: Overcurrent, overvoltage, undercurrent, undervoltage, voltage swell, and voltage dip

- Supports sampled data DMA Transmission, up to 512 points per cycle.

#### Function

- Current sampled: Supports CT and Rogowski coil

- Supports UART Interface

- Operating Temperature: -40 ~ +105°C

- Storage Temperature: -55 ~ +150°C

- Package: SOP16

### Contents

# Contents

| U    | <b>#ang</b> | Vango Technologies, Inc.                   | 4 / 35 |  |  |  |

|------|-------------|--------------------------------------------|--------|--|--|--|

| 4    | 7.3.4       | Frequency Measurement                      |        |  |  |  |

|      | 7.3.3       | B Power Small Signal Calibration           |        |  |  |  |

|      | 7.3.2       | 2 Ratio Difference Calibration             |        |  |  |  |

|      | 7.3.1       | Phase Calibration                          |        |  |  |  |

|      | 7.3         | Calibration                                | 22     |  |  |  |

|      | 7.2         | Features                                   |        |  |  |  |

|      | 7.1         | Overview                                   |        |  |  |  |

| 7    | Measure     | ment Data Processing Unit                  | 22     |  |  |  |

|      | 6.5         | Block Read Operation                       |        |  |  |  |

|      | 6.4         | Write Operation                            |        |  |  |  |

|      | 6.3         | Read Operation                             | 17     |  |  |  |

|      | 6.2         | Communication Protocol                     | 15     |  |  |  |

|      | 6.1         | Overview                                   | 15     |  |  |  |

| 6    | Universa    | I Asynchronous Receiver Transmitter (UART) | 15     |  |  |  |

|      | 5.2         | Software Reset                             |        |  |  |  |

|      | 5.1         | RX Reset                                   | 14     |  |  |  |

| 5    | Reset       |                                            | 14     |  |  |  |

|      | 4.1         | Power-down Monitoring Circuit              | 13     |  |  |  |

| 4    | Power S     | ystem                                      | 13     |  |  |  |

| 3    | Paramete    | ers                                        | 11     |  |  |  |

| 2    | Pin Desc    | ription                                    | 10     |  |  |  |

| 1    | Pin Conf    | iguration                                  | 9      |  |  |  |

| Re   | ision Histo | Dry                                        |        |  |  |  |

| List | of Figure.  |                                            | 7      |  |  |  |

| List | of Tables.  |                                            | 6      |  |  |  |

| Cor  | ntents      |                                            |        |  |  |  |

| Fur  | nction2     |                                            |        |  |  |  |

#### Contents

#### V9160 Datasheet

| 8  | Sampleo             | l data Upload                                            | . 25                 |

|----|---------------------|----------------------------------------------------------|----------------------|

|    | 8.1                 | Overview                                                 | . 25                 |

|    | 8.2                 | Timing and Format                                        | . 25                 |

| 9  | Power C             | Quality Processing Unit                                  | . 27                 |

|    | 9.1                 | Overview                                                 | . 27                 |

|    | 9.2                 | Features                                                 | . 27                 |

|    | 9.3                 | Voltage Swell/ Dip                                       | . 27                 |

|    | 9.4                 | Overvoltage, Undervoltage, Overcurrent, and Undercurrent | . 27                 |

|    |                     |                                                          |                      |

|    | 9.5                 | Zero-Crossing Detection                                  | . 28                 |

| 10 |                     | Zero-Crossing Detection                                  |                      |

| 10 |                     |                                                          | . 30                 |

| 10 | Sig                 | nal Output Port                                          | . 30<br>. 30         |

| 10 | Sig<br>10.1<br>10.2 | nal Output Port<br>Overview                              | . 30<br>. 30<br>. 30 |

# List of Tables

| Table1.                   | Document Version History                                                                                  | 8  |

|---------------------------|-----------------------------------------------------------------------------------------------------------|----|

| Table2.                   | Pin Description                                                                                           | 10 |

| Table3.                   | Parameters                                                                                                | 11 |

| Table4.                   | Power Consumption                                                                                         | 12 |

| Table5.                   | UART Communication Errors                                                                                 | 15 |

| Table6.                   | UART Communication Timing Parameters                                                                      | 16 |

| Table7.<br>Data Bits B7:I | Command Frame Structure Sent by the MCU to V9160 for Read Operation (Only Listing the B0 of Each Byte)    | 17 |

| Table8.<br>Bits B7:B0 of  | Response Frame Structure Sent by V9160 to MCU for Read Operation (Only Listing the Data Each Byte)        | 17 |

| Table9.<br>Data Bits B7:I | Command Frame Structure Sent by the MCU to V9160 for Write Operation (Only Listing the B0 of Each Byte)   | 18 |

| Table10.<br>B7:B0 of eact | Response frame structure sent by V9160 to MCU for write operation (only listing the data bits<br>h byte). | 19 |

| Table11.                  | Block Read Data Sequence                                                                                  | 19 |

| Table12.<br>bits B7:B0 of | Command frame structure sent by MCU to V9160 for block read operation (only listing the data each byte)   |    |

| Table13.<br>bits B7:B0 of | Response frame structure sent by V9160 to MCU for block read operation (only listing the data each byte)  |    |

| Table14.                  | Phase Calibration Description                                                                             | 23 |

| Table15.                  | Relationship Between Sampling Points and Transmission Rate                                                | 25 |

| Table16.                  | Active Waveform Upload Data Format                                                                        | 26 |

| Table17.                  | IO output configuration                                                                                   | 30 |

# List of Figure

| Figure1.  | Power-down Monitoring                             | 13 |

|-----------|---------------------------------------------------|----|

| Figure2.  | RX Reset Timing Diagram during UART Communication | 14 |

| Figure3.  | 11-Bit Byte Data Format (LSB to MSB)              | 15 |

| Figure4.  | Command Frame for Read/Write/Broadcast Operation  | 15 |

| Figure5.  | Timing of UART Communication                      | 16 |

| Figure6.  | Read Operation Communication Protocol             | 17 |

| Figure7.  | Write Operation Communication Protocol            | 18 |

| Figure8.  | Block Read Operation Communication Protocol       | 20 |

| Figure9.  | DMA SPI Transmission Timing                       | 25 |

| Figure10. | Schematic Diagram of Electrical Signal Detection  | 27 |

| Figure11. | Voltage/Current Zero-Crossing Output Diagram2     | 29 |

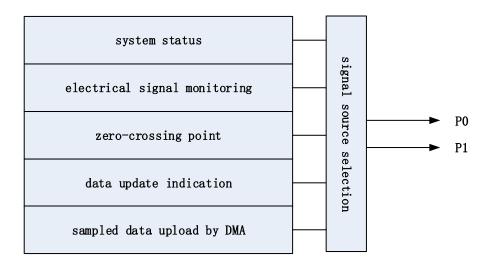

| Figure12. | Functional Block Diagram of Signal Output Port    | 30 |

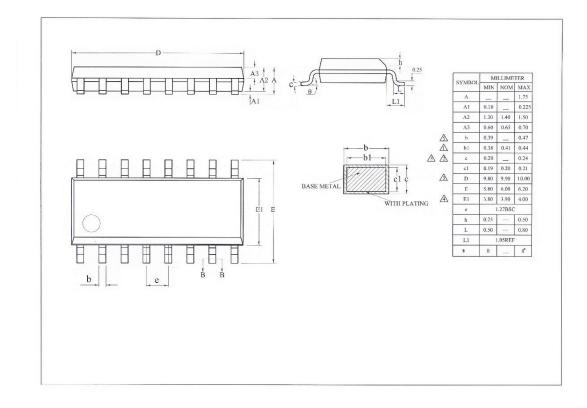

| Figure13. | Outline dimension for V9160                       | 34 |

# **Revision History**

| Date       | Revision | Description                                  |  |

|------------|----------|----------------------------------------------|--|

| 2024.11.18 | V1.0     | Initial Version;                             |  |

| 2025.01.21 | V1.1     | Delete the POR function;                     |  |

| 2025.04.09 | V1.2     | Modify the RCH performance parameter values; |  |

#### Table1.Document Version History

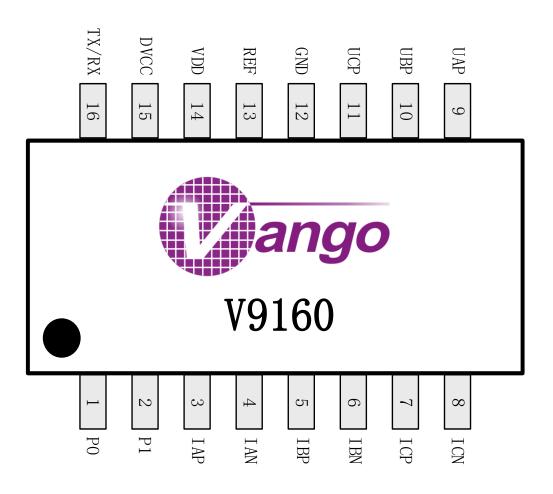

# 1 Pin Configuration

# 2 Pin Description

#### Table2.Pin Description

| Pin Number | Pin Name | Input / Output                       | t Function                           |  |

|------------|----------|--------------------------------------|--------------------------------------|--|

| 1          | P0       | 0                                    | Configurable output                  |  |

| 2          | P1       | 0                                    | Configurable output                  |  |

| 3          | IAP      | 1                                    | Current A channel P-terminal input   |  |

| 4          | IAN      | 1                                    | Current A channel N-terminal input   |  |

| 5          | IBP      | 1                                    | Current B channel P-terminal input   |  |

| 6          | IBN      | 1                                    | I Current B channel N-terminal input |  |

| 7          | ICP      | 1                                    | Current C channel P-terminal input   |  |

| 8          | ICN      | I Current C channel N-terminal input |                                      |  |

| 9          | UAP      | 1                                    | Voltage A channel P-terminal input   |  |

| 10         | UBP      | I Voltage B channel P-terminal input |                                      |  |

| 11         | UCP      | 1                                    | Voltage C channel P-terminal input   |  |

| 12         | GND      | Р                                    | Ground                               |  |

| 13         | REF      | 0                                    | Reference voltage                    |  |

| 14         | VDD      | Р                                    | Main power supply                    |  |

| 15         | DVCC     | O Digital power output               |                                      |  |

| 16         | TX/ RX   | 1/0                                  | UART communication                   |  |

# 3 Parameters

#### Table3. Parameters

| Parameter                                     | Min.     | Тур.  | Max.  | Unit     | Remark                          |

|-----------------------------------------------|----------|-------|-------|----------|---------------------------------|

| Analog Input                                  |          |       |       |          |                                 |

| Maximum Voltage                               | -200     |       | 200   | mV       | Peak value                      |

| Signal channel                                |          |       |       |          |                                 |

| Level Current                                 | -400     |       | 400   |          |                                 |

| channel                                       |          |       |       |          |                                 |

| Bandwidth (-3dB)                              |          | 2     |       | kHz      |                                 |

| On-chip Reference                             |          | -     |       |          |                                 |

| Temperature Coefficie                         | ent      | 10    |       | ppm/°C   |                                 |

| Output Voltage                                | 1.1      | 1.2   | 1.3   | V        |                                 |

| VDD Power-on rate                             | 3.3V/s   |       | 1V/ms |          |                                 |

| PVD                                           |          |       |       |          |                                 |

| Detection Threshold for                       | or 2.7   | 2.8   | 2.9   | V        |                                 |

| Power-Down                                    |          |       |       |          |                                 |

| Hysteresis                                    |          | 30    |       | mV       |                                 |

| Clock Frequency                               | <u> </u> |       |       | <u> </u> |                                 |

| RCH                                           |          | 6.5   |       | MHz      |                                 |

| Phase Error Between                           | Channels |       |       |          |                                 |

| Total Active Energy                           |          | 0.1   |       | %        | Dynamic Range                   |

| Metering Error                                |          |       |       |          | 10000:1 @ 25°C                  |

| Total Active Energy                           |          | 2     |       | kHz      |                                 |

| Metering Bandwidth                            |          |       |       |          |                                 |

| Total Reactive Energy                         | /        | 0.1   |       | %        | Dynamic Range                   |

| Metering Error                                |          | _     |       |          | 10000:1 @ 25°C                  |

| Total Reactive Energy                         | /        | 2     |       | kHz      |                                 |

| Metering Bandwidth                            |          |       |       |          |                                 |

| Fundamental Active                            |          | 0.1   |       | %        | Dynamic Range                   |

| Energy Metering Erro                          | r        | 05    |       |          | 10000:1 @ 25°C                  |

| Fundamental Active                            |          | 65    |       | Hz       |                                 |

| Energy Metering<br>Bandwidth                  |          |       |       |          |                                 |

| Fundamental Reactive                          |          | 0.1   |       | %        | Dunamia Banga                   |

|                                               |          | 0.1   |       | 70       | Dynamic Range<br>10000:1 @ 25°C |

| Energy Metering Error<br>Fundamental Reactive |          | 65    |       | Hz       | 10000.1@25 C                    |

| Energy Metering                               | e        | 05    |       | пг       |                                 |

| Bandwidth                                     |          |       |       |          |                                 |

| Total Apparent Energy                         | /        | 0.2   |       | %        | Dynamic Range 2000:1            |

| Metering Error                                | /        | 0.2   |       | 70       | @ 25°C                          |

| Fundamental Apparer                           | nt       | 0.2   |       | %        | Dynamic Range 2000:1            |

| Energy Metering Error                         |          | 0.2   |       | ,,,      | @ 25°C                          |

| VRMS Metering Error                           |          | 0.2   |       | %        | Dynamic Range 2000:1            |

|                                               |          |       |       |          | @ 25°C                          |

| VRMS Metering                                 |          | 2     |       | kHz      |                                 |

| Bandwidth                                     |          |       |       |          |                                 |

| IRMS Metering Error                           |          | 0.2   |       | %        | Dynamic Range 2000:1            |

|                                               |          | • • • |       |          | @ 25°C                          |

| IRMS Metering                                 |          | 2     |       | kHz      |                                 |

| Bandwidth                                     |          |       |       |          |                                 |

| digital I/O                                   |          |       |       |          |                                 |

| Driving capability 4 mA                       |          |       |       |          |                                 |

#### Parameters

|                          |      | -   |          |    |                    |

|--------------------------|------|-----|----------|----|--------------------|

| Output High Voltage,     | 2.4  |     |          | V  |                    |

| Vон                      |      |     |          |    |                    |

| Output Low Voltage,      |      |     | 0.4      | V  |                    |

| V <sub>OL</sub>          |      |     |          |    |                    |

| Input High Voltage, VINH | 2.0  |     | 3.6      | V  |                    |

| Input Low Voltage, VINL  | -0.3 |     | 0.8      | V  |                    |

| Power Input              |      |     |          |    |                    |

| AVDD                     | 3.0  | 3.3 | 3.6      | V  |                    |

| Digital Power Output (DV | CC)  |     |          |    |                    |

| Voltage                  |      | 1.2 |          | V  |                    |

| Input voltage of current | -0.4 |     | AVDD+0.3 | V  | relative to ground |

| sampling channel         |      |     |          |    | -                  |

| Input voltage of voltage | -0.2 |     | AVDD+0.3 | V  | relative to ground |

| sampling channel         |      |     |          |    | C C                |

| Operating temperature    | -40  |     | +105     | °C |                    |

| Storage temperature      | -55  |     | +150     | °C |                    |

#### Table4.Power Consumption

| Working Mode            | e/Circuit Module       | Power       | Unit | Explanation                                                                                                                                                                                                                    |

|-------------------------|------------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                        | Consumption |      |                                                                                                                                                                                                                                |

| Full-Speed<br>Operation | Normal Working<br>Mode | 8.5         | mA   | The data of the chip's current<br>consumption when the system<br>clock frequency is 26.2144 MHz,<br>the ADC clock frequency is<br>6.5536 MHz, and the ADCs of<br>A/B/C three-phase<br>voltage/current channels are<br>enabled. |

# 4 Power System

The power system of V9160 has the following characteristics:

- 3.3V single power supply, voltage input range: 2.8 3.6V;

- Supports power-down monitoring;

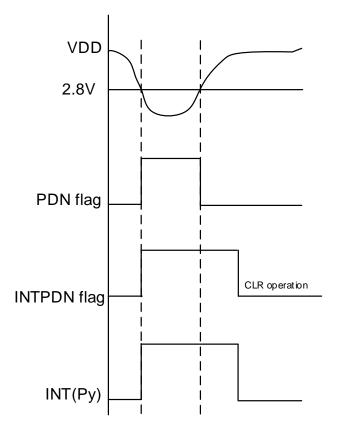

## 4.1 Power-down Monitoring Circuit

The V9160 has a built-in power-down monitoring circuit that can monitor the input signal of the VDD pin in real-time. When the level on the VDD pin is lower than 2.8V, the system generates a power-down interrupt. At this time, the metering accuracy cannot be guaranteed, but normal communication is still possible.

The power-down monitoring circuit is always active.

#### Figure1. Power-down Monitoring

## 5 Reset

Reset

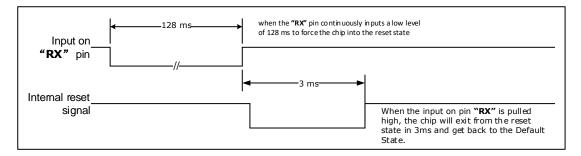

## 5.1 RX Reset

When the "RX" pin is continuously low for 128 ms, the chip generates an internal reset. After that, when the "RX" pin is high, the chip reset is completed after 3 ms.

Attention: A RX reset operation needs to be performed after the chip is powered on.

Figure2. RX Reset Timing Diagram during UART Communication

In the reset state, the external cannot access the RAM. After the system exits the reset state, the RAM performs a self-check that lasts approximately 0.35ms. After the self-check passes, the RAM can be freely accessed.

After the system exits the reset state and the RAM initialization is completed, the UART immediately starts working.

## 5.2 Software Reset

Executing the soft reset function can cause an internal reset of the chip, and the reset will be completed after 1ms.

Ensure that the system communication is normal before executing the software reset function.

#### 6.1 Overview

The V9160 supports UART communication. After a POR reset, RX reset, or soft reset, the V9160 defaults to using UART communication. The V9160 UART is a standard 8-bit UART with odd parity. The UART uses low-byte-first and low-bit-first transmission. The following figure shows the standard format of a UART byte.

#### Figure3. 11-Bit Byte Data Format (LSB to MSB)

The UART protocol is a half-duplex protocol. After the MCU finishes sending a command, the V9160 uploads data after 1ms (depending on the accuracy of the system clock). The V9160 UART supports adaptive baud rate and recommends using a baud rate of 1200bps - 19200bps. The V9160 automatically adapts to the communication baud rate by receiving the first frame header. This baud rate is also fine-tuned during subsequent communications. If the communication baud rate changes significantly, the baud rate adaptation needs to be performed again.

The V9160 supports a continuous write communication command, which can save parameter configuration time.

Under the following conditions, the UART reception of the V9160 stops.

#### Table5.UART Communication Errors

| Number | Conditions                                                                                                                                  | UART_ERR Set to 1 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1      | Frame header error in UART reception.                                                                                                       | No                |

| 2      | UART reception timeout, the time interval between two consecutive bytes is greater than 20ms (related to the accuracy of the system clock). | Yes               |

| 3      | Odd parity bit error in UART reception.                                                                                                     | Yes               |

| 4      | Checksum byte error in UART reception.                                                                                                      | Yes               |

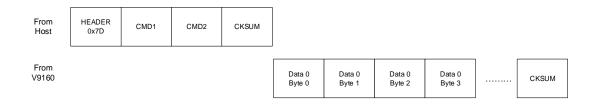

## 6.2 Communication Protocol

In read, write or block read communication, the master MCU needs a command frame that is composed of 8 data bytes to operate a 32-bit data in the V9160.

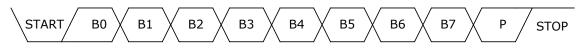

#### Figure 4. Command Frame for Read/Write/Broadcast Operation

In read or write operation, when the V9160 receives the command frame from the master MCU, it will reply to the master MCU with a respond frame of different structures. In broadcast communication, the V9160 will not reply to the master MCU to avoid communication conflict.

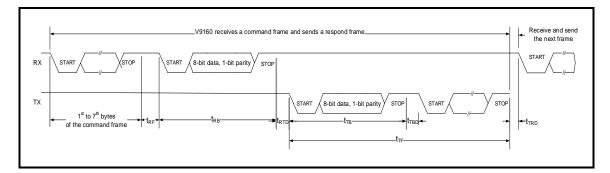

The following figure depicts the timing of UART communication.

#### Figure5. Timing of UART Communication

#### Table6. UART Communication Timing Parameters

| Parameter        | Description                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>RB</sub>  | Time to receive a data byte on pin RX.                                                                                                                                                       |

|                  | $t_{RB} = \frac{11}{baudrate}$                                                                                                                                                               |

|                  | Where, <i>baudrate</i> is the actual baud rate.                                                                                                                                              |

| t <sub>RF</sub>  | The maximum time between two bytes when receiving a command frame on pin " <b>RX</b> "                                                                                                       |

|                  | t <sub>RF</sub> =20ms                                                                                                                                                                        |

|                  | After a timeout event, the UART interface is idle and waits for the next command frame.                                                                                                      |

| t <sub>rtd</sub> | The delay between command frame reception on pin RX and respond frame transmission on pin TX.                                                                                                |

|                  | Please note no respond frame will be transmitted in broadcast communication,<br>and at least 1ms delay is recommended between two continuous command<br>frames for broadcast communications. |

| t⊤F              | Time to transmit a respond frame in read or write operation, depending on the structure of the frame.                                                                                        |

| tтв              | Time to transmit a data byte.                                                                                                                                                                |

|                  | $t_{TB} = \frac{11}{baudrate}$                                                                                                                                                               |

|                  | Where <i>baudrate</i> is the actual baud rate.                                                                                                                                               |

| tтвD             | Delay between two continuous data bytes in a respond frame.                                                                                                                                  |

|                  | 0ms≤t <sub>TBD</sub> ≤20ms                                                                                                                                                                   |

| t <sub>TRD</sub> | The delay between respond frame transmission on pin TX and the next command frame reception on pin RX. More than 1ms is recommended.                                                         |

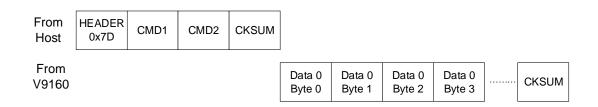

## 6.3 Read Operation

- Supports reading 1 ~ 16 consecutive registers.

- The V9160 will respond.

#### Figure6. Read Operation Communication Protocol

# Table7.Command Frame Structure Sent by the MCU to V9160 for Read Operation (Only Listing the<br/>Data Bits B7:B0 of Each Byte)

| Sequence | Byte   | B7                                                                                                                                                                              | B6                                                                                                                        | В5         | B4      | B3 | B2 | B1 | B0 |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------|---------|----|----|----|----|

| 1        | HEADER | 0                                                                                                                                                                               | 1                                                                                                                         | 1          | 1       | 1  | 1  | 0  | 1  |

| 2        | CMD1   | 0: Read 2<br>1: Read 2                                                                                                                                                          | Read operation length selection (N)<br>0: Read 1 32-Bits data.<br>1: Read 2 32-Bits data.<br><br>15: Read 16 32-Bits data |            |         |    |    | 0  | 1  |

| 3        | CMD2   | Read ope                                                                                                                                                                        | eration star                                                                                                              | ting addre | ss (D0) |    |    |    |    |

| 4        | CKSUM  | Checksum. Calculation method: Add CMD1 and CMD2 byte by byte,<br>take the inverse of the sum, and then add 0x33. The formula is as<br>follows:<br>CKSUM = 0x33 + ~(CMD1 + CMD2) |                                                                                                                           |            |         |    |    |    |    |

# Table8.Response Frame Structure Sent by V9160 to MCU for Read Operation (Only Listing the<br/>Data Bits B7:B0 of Each Byte)

| Sequence | Byte             | B7                                                                         | B6                                                                        | B5         | B4       | В3        | B2         | B1       | В0      |  |  |

|----------|------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|----------|-----------|------------|----------|---------|--|--|

| 1        | Data 0<br>Byte 0 | Bit[7:0]                                                                   | Bit[7:0] of the target data read from the register (address D0)           |            |          |           |            |          |         |  |  |

| 2        | Data 0<br>Byte 1 | Bit[15:8]                                                                  | Bit[15:8] of the target data read from the register (address D0)          |            |          |           |            |          |         |  |  |

| 3        | Data 0<br>Byte 2 | Bit[23:1                                                                   | Bit[23:16] of the target data read from the register (address D0)         |            |          |           |            |          |         |  |  |

| 4        | Data 0<br>Byte 3 | Bit[31:24                                                                  | Bit[31:24] of the target data read from the register (address D0)         |            |          |           |            |          |         |  |  |

| 4xN+1    | Data N<br>Byte 0 | Bit[7:0]                                                                   | of the tar                                                                | get data r | ead from | the regis | ter (addre | ess DN = | D0 + N) |  |  |

| 4xN+2    | Data N<br>Byte 1 | Bit[15:8]<br>N)                                                            | Bit[15:8] of the target data read from the register (address DN = D0 + N) |            |          |           |            |          |         |  |  |

| 4xN+3    | Data N<br>Byte 2 | Bit[23:16] of the target data read from the register (address DN = D0 + N) |                                                                           |            |          |           |            |          |         |  |  |

| 4xN+4    | Data N<br>Byte 3 | Bit[31:24] of the target data read from the register (address DN = D0 + N) |                                                                           |            |          |           |            |          |         |  |  |

| -           |                                                                                              |                                                                   |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| 4xN+5       | CKSUM                                                                                        | Checksum. Calculation method: Add the 4×(N + 1) target data bytes |  |  |  |  |

|             |                                                                                              | (Data 0 - N Byte 0 - 3, from V9160) and CMD1 and CMD2 (from MCU)  |  |  |  |  |

|             |                                                                                              | byte by byte, take the inverse of the sum, and then add 0x33. The |  |  |  |  |

|             |                                                                                              | formula is as follows:                                            |  |  |  |  |

|             |                                                                                              | CKSUM = 0x33 + ~(CMD1 + CMD2 + Data 0 Byte 0 + Data 0 Byte 1 +    |  |  |  |  |

|             |                                                                                              | Data 0 Byte 2 + Data 0 Byte 3 + + Data N Byte 0 + Data N Byte 1 + |  |  |  |  |

|             |                                                                                              | Data N Byte 2 + Data N Byte 3)                                    |  |  |  |  |

| When the re | When the read operation length N is equal to 0, the V9160 will only send a 5 - byte response |                                                                   |  |  |  |  |

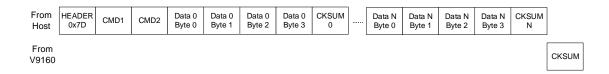

## 6.4 Write Operation

frame to the MCU.

- Supports writing 1 ~ 16 consecutive registers.

- The V9160 will respond.

#### Figure7. Write Operation Communication Protocol

# Table9.Command Frame Structure Sent by the MCU to V9160 for Write Operation (Only Listing<br/>the Data Bits B7:B0 of Each Byte)

| Sequence | Byte             | B7                                                                                                                                                                                                                                                                                                               | <b>B</b> 6 | B5     | B4     | B3      | B2     | B1    | В0   |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|--------|---------|--------|-------|------|

| 1        | HEADER           | 0                                                                                                                                                                                                                                                                                                                | 1          | 1      | 1      | 1       | 1      | 0     | 1    |

| 2        | CMD1             | Write length selection (N):<br>0: Write 1 32-bit data.<br>1: Write 2 32-bit data.<br><br>15: Write 16 32-bit data.                                                                                                                                                                                               |            |        |        | 0       | 0      | 1     | 0    |

| 3        | CMD2             | Write operation starting add                                                                                                                                                                                                                                                                                     | fress      | (D0).  |        |         |        |       |      |

| 4        | Data 0<br>Byte 0 | Bit[7:0] of the target data w                                                                                                                                                                                                                                                                                    | ritten     | to the | e regi | ster (a | addre  | ss D0 | ).   |

| 5        | Data 0<br>Byte 1 | Bit[15:8] of the target data written to the register (address D0).                                                                                                                                                                                                                                               |            |        |        |         |        |       |      |

| 6        | Data 0<br>Byte 2 | Bit[23:16] of the target data                                                                                                                                                                                                                                                                                    | writte     | en to  | the re | egiste  | r (add | lress | D0). |

| 7        | Data 0<br>Byte 3 | Bit[31:24] of the target data                                                                                                                                                                                                                                                                                    | writte     | en to  | the re | egiste  | r (add | lress | D0). |

| 8        | CKSUM 0          | Checksum 0. Calculation method: Add the above 4 target data<br>bytes (Data 0 Byte 0 - 3) and CMD1 and CMD2 byte by byte,<br>take the inverse of the sum, and then add 0x33. The formula is<br>as follows:<br>CKSUM 0 = 0x33 + ~(CMD1 + CMD2 + Data 0 Byte 0 + Data 0<br>Byte 1 + Data 0 Byte 2 + Data 0 Byte 3). |            |        |        |         |        |       |      |

|          |                  |                                                                                                                                                                                                                                                                                                                  |            |        |        |         |        |       |      |

| 5xN+4    | Data N<br>Byte 0 | Bit[7:0] of the target data written to the register (address DN = D0 + N).                                                                                                                                                                                                                                       |            |        |        |         |        | 1 =   |      |

#### V9160 Datasheet

| 5xN+5      | Data N               | Bit[15:8] of the target data written to the register (address DN =                                                                                                                                                                                                                                                                                                                                     |

|------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Byte 1               | D0 + N).                                                                                                                                                                                                                                                                                                                                                                                               |

| 5xN+6      | Data N               | Bit[23:16] of the target data written to the register (address DN                                                                                                                                                                                                                                                                                                                                      |

|            | Byte 2               | = D0 + N).                                                                                                                                                                                                                                                                                                                                                                                             |

| 5xN+7      | Data N               | Bit[31:24] of the target data written to the register (address DN                                                                                                                                                                                                                                                                                                                                      |

|            | Byte 3               | = D0 + N).                                                                                                                                                                                                                                                                                                                                                                                             |

| 5xN+8      | CKSUM N              | Checksum N (from MCU). Calculation method: Add the $4 \times (N + 1)$ target data bytes (Data 0 - N Byte 0 - 3) and CMD1 and CMD2 byte by byte, take the inverse of the sum, and then add 0x33. The formula is as follows:<br>CKSUM N = $0x33 + \sim (CMD1 + CMD2 + Data 0 Byte 0 + Data 0 Byte 1 + Data 0 Byte 2 + Data 0 Byte 3 + + Data N Byte 0 + Data N Byte 1 + Data N Byte 2 + Data N Byte 3).$ |

| When the w | vrite operation leng | th N is equal to 0, the MCU only needs to send the first 8 bytes                                                                                                                                                                                                                                                                                                                                       |

|            | nand frame to the    |                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |                      | və 100.                                                                                                                                                                                                                                                                                                                                                                                                |

# Table10.Response frame structure sent by V9160 to MCU for write operation (only listing the data<br/>bits B7:B0 of each byte).

| Sequence | Byte  | B7                             | B6                                        | B5        | B4                                | B3      | B2          | B1         | B0      |

|----------|-------|--------------------------------|-------------------------------------------|-----------|-----------------------------------|---------|-------------|------------|---------|

| 1        | CKSUM | success<br>If CKSU<br>is succe | ful.<br>M is equa<br>ssful.<br>M is not e | al to CKS | Used to c<br>UM N (fro<br>CKSUM N | om MCU) | , then this | s write op | eration |

## 6.5 Block Read Operation

To facilitate users to read the required data at once and improve communication efficiency, the V9160 provides a fixed continuous read function.

Features are as follows:

- Support block read operations on registers with fixed addresses that are not continuous.

- When the current phase measurement mode is single-phase measurement mode, after the UART block read is completed, a single-phase measurement is automatically triggered.

- V9160 will respond.

- The fixed return data order of block read registers is shown in the following table.

#### Table11.Block Read Data Sequence

| Number | Data Item                                         |

|--------|---------------------------------------------------|

| 0      | Average active power value of phase A full wave   |

| 1      | Average active power value of phase B full wave   |

| 2      | Average active power value of phase C full wave   |

| 3      | Average reactive power value of phase A full wave |

| 4      | Average reactive power value of phase B full wave |

| 5      | Average reactive power value of phase C full wave |

| 6      | Average apparent power value of phase A full wave |

| 7      | Average apparent power value of phase B full wave |

| 8  | Average apparent power value of phase C full wave |

|----|---------------------------------------------------|

| 9  | Average RMS voltage value of phase A full wave    |

| 10 | Average RMS voltage value of phase B full wave    |

| 11 | Average RMS voltage value of phase C full wave    |

| 12 | Average RMS current value of phase A full wave    |

| 13 | Average RMS current value of phase B full wave    |

| 14 | Average RMS current value of phase C full wave    |

| 15 | Average frequency value of phase A full wave      |

| 16 | Average frequency value of phase B full wave      |

| 17 | Average frequency value of phase C full wave      |

| 18 | Phase angle of phase B voltage                    |

| 19 | Phase angle of phase C voltage                    |

| 20 | Phase angle of phase A current                    |

| 21 | Phase angle of phase B current                    |

| 22 | Phase angle of phase C current                    |

| 23 | Chip status register STS1                         |

| 24 | Baud rate measurement value DAT_BAUDCNT8          |

#### Figure8. Block Read Operation Communication Protocol

# Table12.Command frame structure sent by MCU to V9160 for block read operation (only listing the<br/>data bits B7:B0 of each byte).

| Sequence | Byte   | B7                                                                                                                                                                         | B6 | B5 | B4                                                                                                                                                                                                                                                                                                                                                                                                                      | B3 | B2 | B1 | В0 |  |

|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|--|

| 1        | HEADER | 0                                                                                                                                                                          | 1  | 1  | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | 1  | 1  | 0  | 1  |  |

| 2        | CMD1   | 0                                                                                                                                                                          | 0  | 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 0  | 0  | 1  | 1  |  |

| 3        | CMD2   | 0                                                                                                                                                                          | 0  | 0  | 0       0       1       1         Starting sequence number selection for block read operation (M).         For example: If M = 3, the first returned data is the average reactive power value of phase A full wave.         If M = 0, the first returned data is the average active power value of phase A full wave.         If M = 0, the first returned data is the average active power value of phase A full wave. |    |    |    |    |  |

| 4        | CKSUM  | Checksum. Calculation method: Add CMD1 and CMD2 byte by byte, take the inverse of the sum, and then add 0x33. The formula is as follows:<br>CKSUM = 0x33 + ~(CMD1 + CMD2). |    |    |                                                                                                                                                                                                                                                                                                                                                                                                                         |    |    |    |    |  |

# Table13.Response frame structure sent by V9160 to MCU for block read operation (only listing the<br/>data bits B7:B0 of each byte).

| Sequence | Byte             | B7                 | B6 | B5        | B4        | B3        | B2         | B1        | B0     |

|----------|------------------|--------------------|----|-----------|-----------|-----------|------------|-----------|--------|

| 1        | Data 0<br>Byte 0 | Bit[7:0]<br>number |    | rget data | read from | m the blo | ck read re | gister se | quence |

#### V9160 Datasheet

| Sequence | Byte             | B7                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>B6</b>                                                                                  | B5 | B4         | B3        | B2         | B1        | В0     |  |  |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----|------------|-----------|------------|-----------|--------|--|--|

| 2        | Data 0<br>Byte 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit[15:8] of the target data read from the block read register sequence number M.          |    |            |           |            |           |        |  |  |

| 3        | Data 0<br>Byte 2 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6] of the<br>ce numb                                                                       |    | ata read f | rom the t | olock read | register  |        |  |  |

| 4        | Data 0<br>Byte 3 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4] of the<br>ce numb                                                                       |    | ata read f | rom the t | olock read | register  |        |  |  |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            |    |            |           |            |           |        |  |  |

| 4xN+1    | Data N<br>Byte 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | of the ta<br>(M + N)                                                                       |    | read fro   | m the blo | ck read re | gister se | quence |  |  |

| 4xN+2    | Data N<br>Byte 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit[15:8] of the target data read from the block read register sequence number $(M + N)$ . |    |            |           |            |           |        |  |  |

| 4xN+3    | Data N<br>Byte 2 | Bit[23:16] of the target data read from the block read register sequence number $(M + N)$ .                                                                                                                                                                                                                                                                                                                                                   |                                                                                            |    |            |           |            |           |        |  |  |

| 4xN+4    | Data N<br>Byte 3 |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            |    |            | rom the t | olock read | register  |        |  |  |

| 4xN+5    | CKSUM            | sequence number (M + N).<br>Checksum.<br>Calculation method: Add the 4×(N + 1) target data bytes (Data 0 - N<br>Byte 0 - 3, from V9160) and CMD1 and CMD2 (from MCU) byte by<br>byte, take the inverse of the sum, and then add 0x33. The formula is<br>as follows:<br>CKSUM = 0x33 + ~(CMD1 + CMD2 + Data 0 Byte 0 + Data 0 Byte 1<br>+ Data 0 Byte 2 + Data 0 Byte 3 + + Data N Byte 0 + Data N Byte<br>1 + Data N Byte 2 + Data N Byte 3). |                                                                                            |    |            |           |            |           |        |  |  |

|          |                  | When the read operation sequence number is greater than or equal to 24, the V9160 will only send a 5-byte response frame to the MCU.                                                                                                                                                                                                                                                                                                          |                                                                                            |    |            |           |            |           |        |  |  |

8. Measurement Data Processing Unit

# 7 Measurement Data Processing Unit

#### 7.1 Overview

The MDPU is mainly used to calculate the full-wave and fundamental active power, full-wave and fundamental reactive power, full-wave and fundamental apparent power, full-wave and fundamental RMS values, full-wave and fundamental combined phase power, line voltages, and provides grid event monitoring functions. It also provides original waveform data, which can be output through DMA.

### 7.2 Features

- Supports simultaneous metering of 3 voltage channels and 3 current channels.

- Provides various measurement data:

- 6 channels voltage/ current signal original waveforms (22-bit), output in DMA mode

- DC components of 6 channels voltage / current signals, full-wave/ fundamental RMS values and active/ reactive/ apparent power of each phase

- 3 channels line voltages

- Frequency/ phase/ power factor

- Line voltage measurement data between each phase

- Selectable full-wave bandwidth.

- Supports software calibration:

- Supports waveform pre-calibration

- Supports ratio error correction and secondary compensation (offset correction) for full-/ fundamental active power, reactive power, and fundamental active power

- Selectable refresh time for average power value or average RMS value.

- Provides 10-cycle or 12-cycle average RMS values for voltage flicker detection.

- Supports judgment of voltage swell/ dip, overvoltage/ undervoltage, and overcurrent/ undercurrent.

### 7.3 Calibration

#### 7.3.1 Phase Calibration

$N = Round(C \times E)$

Where:

C: the constant coefficient for angle difference calibration;

*N*: the value written into the register related to angle difference calibration, with a sign. It is represented in two's complement.

*E*: the error displayed on the test bench.

#### Table14. Phase Calibration Description

| MODE | calibration accuracy(degree) | Calibration range(degree) |

|------|------------------------------|---------------------------|

| 0x00 | 0.00274658203125             | ±1.93084716796875         |

For MODE = 0x00, the offset is within the range of 0 to 7, the fine adjustment precision is  $0.00274658203125^{\circ}$ , and the fine adjustment range is  $\pm 0.17303466796875^{\circ}$ . For medium adjustment, the offset is within the range of 0 - 3, the medium adjustment precision is  $0.3515625^{\circ}$ , and the medium adjustment range is  $\pm 1.0546875^{\circ}$ . For coarse adjustment, the offset is within the range of 0 - 1, the coarse adjustment precision is  $0.703125^{\circ}$ , and the coarse adjustment range is  $\pm 0.703125^{\circ}$ .

Phase correction of IA phc\_ia = Angle to be corrected /calibration\_acuracy

Phase correction of IB phc\_ib = Angle to be corrected /calibration\_acuracy

IA and IB error correction values are combined in complement form and written into the error correction register.

#### 7.3.2 Ratio Difference Calibration

$$S = 2^{31} \left( \frac{1}{1+e} - 1 \right) + S1 \left( \frac{1}{1+e} \right)$$

Where:

*S*: the value written into the register for effective value / power ratio difference calibration, in two's complement;

*S*1: the original ratio difference value, that is, the original value displayed on the uncalibrated effective power ratio difference calibration register, in two's complement;

*e*: the error. When performing power ratio difference calibration, e is the error value (E) displayed on the test bench.

#### 7.3.3 Power Small Signal Calibration

$$C = -E \times P \times a\%$$

Where:

E: when the power factor is 1.0, the error displayed on the test bench when a%lb is passed through the test bench;

P: the value of the power register.

#### 7.3.4 Frequency Measurement

Frequency measurement involves zero-crossing detection and counting of the fundamental wave signal. Whenever a positive zero-crossing event occurs, the current count value is latched as the instantaneous frequency measurement value (the number of points in one cycle), and it is determined according to the configuration whether to reset the counter to 1 to start counting again. If it is directly reset, it is the instantaneous frequency measurement value.

The average frequency of any required number of cycles can be obtained by accumulating the instantaneous frequency measurement values through the configuration register counter.

$f = \text{result_freq} \times (\text{cfg_frq_unit_sel} + 1)/f_\text{clk}$

where,

f\_clk: System clock frequency.

result\_freq: Output frequency counting result.

$cfg\_frq\_unit\_sel:$  Selection of the average period for measuring frequency.

# 8 Sampled data Upload

#### 8.1 Overview

The V9160 supports the DMA mode data transmission method and sends a maximum of 6 channels of original sampled data to the external MCU in the SPI protocol master mode. The data upload rate varies depending on the number of sampling points. Before enabling the sampled data active upload function, it is necessary to turn on the sampled data upload switches of the corresponding channels. The switches between each channel are independent. Configure the sampled data upload IO ports P0/ P1 through the IO configuration function.

Table15.

Relationship Between Sampling Points and Transmission Rate

| Sampling Points  | Transmission Rate            |

|------------------|------------------------------|

| 512 points/cycle | Half-frequency division      |

| 256 points/cycle | Quarter-frequency division   |

| 128 points/cycle | Eighth-frequency division    |

| 64 points/cycle  | Sixteenth-frequency division |

The triggering methods for uploading sampled data of V9160 support command-triggered and event-triggered. The event-triggered cases include all the following situations: swell and dip events of UA/ UB/ UC, overvoltage and undervoltage events of UA/ UB/ UC, and overcurrent and undercurrent events of IA/ IB/IC.

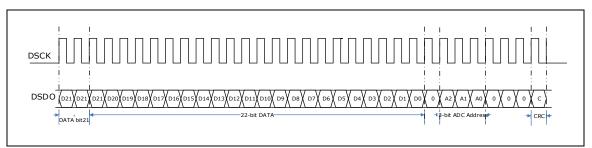

## 8.2 Timing and Format

The V9160 can transmit the original sampled data of the signal to the peripheral device through the DMA SPI interface. The SPI polarity and phase can be configured. When the polarity is 0 and the phase is 0, the transmission timing is as follows:

#### Figure9. DMA SPI Transmission Timing

Transmission method: Complete the transmission of 32-bit data at a time. The format of each transmitted data frame is shown in the following table:

#### Sampled data Upload

#### Table16. Active Waveform Upload Data Format

| Bit  | Content                                                                                 |  |  |

|------|-----------------------------------------------------------------------------------------|--|--|

| 31   | The same value as Bit 29                                                                |  |  |

| 30   | The same value as Bit 29                                                                |  |  |

| 29:8 | Original sampled data of each channel ADC signal, 22-bit                                |  |  |

| 7    | 0                                                                                       |  |  |

| 6    | Indicates whether the current sampled data comes from the UA channel<br>0: No<br>1: Yes |  |  |

| 5    | Indicates whether the current sampled data comes from the IA channel<br>0: No<br>1: Yes |  |  |

| 4    | Indicates whether the current sampled data comes from the UB channel<br>0: No<br>1: Yes |  |  |

| 3    | Indicates whether the current sampled data comes from the IB channel<br>0: No<br>1: Yes |  |  |

| 2    | Indicates whether the current sampled data comes from the UC channel<br>0: No<br>1: Yes |  |  |

| 1    | Indicates whether the current sampled data comes from the IC channel<br>0: No<br>1: Yes |  |  |

| 0    | Parity bit, the parity check range is the first 31 bits                                 |  |  |

## 9 Power Quality Processing Unit

#### 9.1 Overview

Power quality processing unit mainly includes the detection of overvoltage, overcurrent, undervoltage, and undercurrent of voltage/current, as well as the detection of swell/dip of the voltage channel.

### 9.2 Features

- DIP/SWELL

- Detect the swell and dip of the instantaneous effective values of the three-phase voltages A, B, and C.

- Generate the flag bits and interrupts for the swell and dip of the voltage effective value, and the end flag bits and interrupts for the swell and dip.

- Record the maximum swell and dip time.

- Record the values at the maximum swell and dip.

- Overvoltage/ Undervoltage/ Overcurrent/ Under-current

- Realize the instantaneous overcurrent and undercurrent detection of the current and the overvoltage and undervoltage detection of the instantaneous voltage.

- Realize the flag bits and interrupts for overvoltage, undervoltage, overcurrent, and undercurrent.

## 9.3 Voltage Swell/ Dip

The V9160 can be programmed to indicate the swell and dip of the three-phase voltage channels.

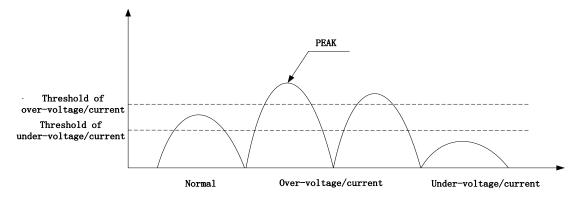

## 9.4 Overvoltage, Undervoltage, Overcurrent, and Undercurrent

#### Figure10. Schematic Diagram of Electrical Signal Detection

#### **Power Quality Processing Unit**

The number of sampling points above the upper threshold: For example, if the set value is 4, it means that if more than 4 points in a half-cycle sampling point exceed the threshold, the waveform of that half-cycle is considered to be over the limit.

The number of half-cycles above the upper threshold: For example, if it is set to 2, it means that if two consecutive half-cycles are both over the limit, an overvoltage or overcurrent event is considered to occur.

The number of sampling points below the lower threshold: For example, if it is set to 4, if it is found that less than or equal to 4 points in a half-cycle sampling point are higher than the lower threshold, the half-cycle is considered to be below the lower limit.

The number of half-cycles below the lower limit: For example, if it is set to 2, it means that if two consecutive half-cycles are both below the lower limit, an undervoltage or undercurrent event is considered to occur.

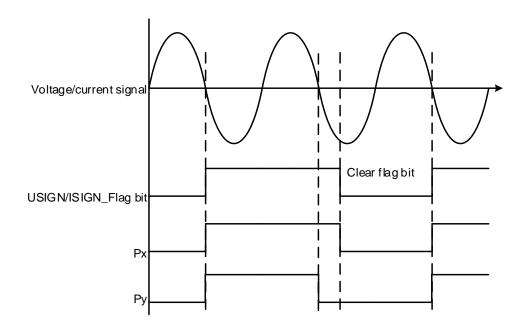

## 9.5 Zero-Crossing Detection

The V9160 supports zero-crossing detection for 3 voltage channels and 3 current channels. The zero-crossing direction can be selected. When a zero-crossing event occurs in the voltage/ current channel signal, the voltage zero-crossing flag bit and the current zero-crossing flag bit in the system interrupt status register will be set to 1. The user needs to write 1 to clear them.

When enabling the voltage/ current zero-crossing interrupt output, configure the voltage/current zero-crossing interrupt output through the IO configuration function. The output level of the pin Px automatically flips according to the voltage zero-crossing flag bit and the current zero-crossing flag bit.

The zero-crossing detection accuracy is related to the choice of sampling points. If there are 256 points in one cycle, the accuracy is 360/256.

Configure the voltage/current zero-crossing output square wave through the IO configuration function. The output level of the pin Py automatically flips in real-time according to the voltage/current zero-crossing state. Every time a zero-crossing event occurs, the IO port flips

once. Since the zero-crossing square wave passes through a band-pass filter, there will be a phase lag between the output and the input, and the delay time is about 8ms (related to the fundamental frequency).

When performing voltage/current zero-crossing detection, the system will also provide a voltage/current threshold detection function. The system will automatically compare whether the instantaneous effective value of the voltage/current exceeds the threshold. If it does not exceed the threshold, it will be judged as an invalid input, and the voltage/current zero-crossing interrupt output and zero-crossing output will be masked until the instantaneous effective value of the voltage/current exceeds the threshold.

The following figure shows the configuration for enabling the zero-crossing interrupt output and the waveforms of the voltage/current zero-crossing flag bits, zero-crossing interrupt output, and zero-crossing output square wave when the zero-crossing detection method is selected as negative zero-crossing.

#### Figure11. Voltage/Current Zero-Crossing Output Diagram

# 10 Signal Output Port

### 10.1 Overview

The V9160 provides at most 2 output signals (P0/P1) for mapping internal output signal sources.

## **10.2** Functional Description

The 2 signal output ports can be configured as the DMA channel interface for sampled data active upload, zero-crossing square wave, and four types of interrupt outputs. The signal output port can be set to output a single signal or several types of interrupt signals.

#### Figure12. Functional Block Diagram of Signal Output Port

| Note1: | When used as an interrupt event output port, the output port defaults to a low-level output. If an event occurs, it outputs a high level until the user clears the event flag bit, and the output state returns to the default level.        |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note2: | When used as a zero-crossing square wave output, the output port defaults to a low-level output. If<br>configured as a positive zero-crossing, the IO port flips when the signal transitions from a negative signal to<br>a positive signal. |

| Note3: | When used as a DMA output port, the SPI protocol is used, and the user needs to select the SPCK and SPDO ports.                                                                                                                              |

| Note4: | The IO output configuration has 8 bits, and the output interrupt type is determined according to the following table:                                                                                                                        |

#### Table17. IO output configuration

|   | Bit6 - Bit3 | Bit2 - Bit0 | Function |

|---|-------------|-------------|----------|

| _ |             |             |          |

| 0 | 0 | High impedance state                             |

|---|---|--------------------------------------------------|

| 0 | 1 | High impedance state                             |

| 0 | 2 | High impedance state                             |

| 0 | 3 | High impedance state                             |

| 0 | 4 | High impedance state                             |

| 0 | 5 | High impedance state                             |

| 0 | 6 | UA voltage dip interrupt                         |

| 0 | 7 | UA voltage swell interrupt                       |

| 1 | 0 | UB voltage dip interrupt                         |

| 1 | 1 | UB voltage swell interrupt                       |

| 1 | 2 | UC voltage dip interrupt                         |

| 1 | 3 | UC voltage swell interrupt                       |

| 1 | 4 | UA voltage dip end interrupt                     |

| 1 | 5 | UA voltage swell end interrupt                   |

| 1 |   |                                                  |

| 1 | 6 | UB voltage dip end interrupt                     |

| 1 | 7 | UB voltage swell end interrupt                   |

| 2 | 0 | UC voltage dip end interrupt                     |

| 2 | 1 | UC voltage swell end interrupt                   |

| 2 | 2 | UA overvoltage interrupt                         |

| 2 | 3 | UA undervoltage interrupt                        |

| 2 | 4 | UB overvoltage interrupt                         |