Specifications are subject to change without notice.

© 2021 Vango Technologies, Inc.

This document contains information that is proprietary to Vango Technologies, Inc.

Unauthorized reproduction of this information in whole or in part is strictly prohibited.

# **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                     |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2015.04.22 | 0.1     | Initial release                                                                                                                                                                                                                                                 |

| 2016.02.22 | 0.2     | <ul> <li>Modified total/fundamental active/reactive power calculation equations: Equation 7-9, Equation 7-10, Equation 7-11, and Equation 7-12</li> <li>Modified "Ai" and "Au" to the peak values of current/voltage inputs in 7.7 Power Calculation</li> </ul> |

| 2018.03.12 | 5.0     | • In order to obtain the best metering performance and temperature performance during normal metering, Bandgap Circuit must be configured according to the calculated result. The calculation method, please refer to Bandgap Circuit chapter.                  |

| 2018.05.31 | 5.1     | Modify the formula of Phase Compensation.                                                                                                                                                                                                                       |

| 2019.04.09 | 7.0     | <ul> <li>Modify the storage temperature to -55~150°C</li> <li>Modify Absolute Maximum Ratings</li> <li>Modify Calibration Step</li> </ul>                                                                                                                       |

| 2021.04.19 | 7.1     | Update IEC Standard                                                                                                                                                                                                                                             |

## **Features**

- 5 V power supply:  $3.0 \text{ V} \sim 5.5 \text{ V}$

- Reference: 1.188 V (Typical drift 10 ppm/°C)

- Typical power dissipation in full operation:

1.5 mA

- Highly metering accuracy:

- ✓ Supporting the requirements of IEC 62053-21:2020/ IEC 62053-22:2020 and IEC 62053-23:2020.

- ✓ Less than 0.1% error in active energy metering over a dynamic range of 5000:1

- ✓ Less than 0.1% error in reactive energy metering over a dynamic range of 3000:1

- Two independent oversampling  $\Sigma/\Delta$  ADCs: One for voltage and one for current

- Various measurements:

- ✓ DC components of voltage and current signals

- ✓ Total and fundamental raw/instantaneous /average current and voltage RMS

- ✓ Total and fundamental raw/instantaneous /average active and reactive power

- ✓ Line frequency

- Supporting current detection

- Supporting UART serial interface, configurable baud rate

- Current input: Shunt resistor/CT

- Crystal frequency: 6.5536 MHz or 3.2768 MHz

- Operating temperature: -40°C ~ +85°C

- Storage temperature: -55°C ~ +150°C

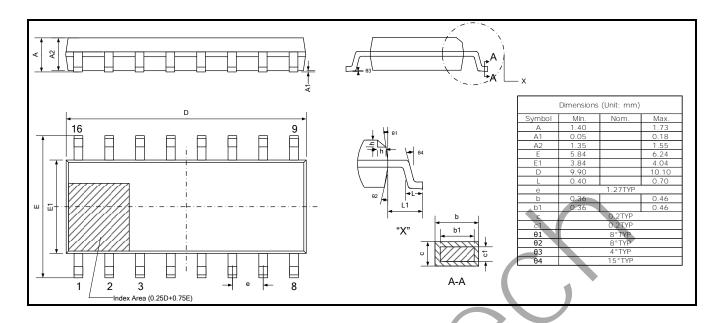

- Package: 16-SOP

- Built-in WDT

# **Specifications**

All maximum/minimum specifications apply over the entire recommended operation range (T = -40 °C  $\sim$  +85 °C, VDD5 = 5 V  $\pm$ 10%) unless otherwise noted. All typical specifications are at TA = 25 °C, VDD5 = 5 V, unless otherwise noted.

| Parameter                         | Min. | Тур.  | Max. | Unit   | Remark                          |

|-----------------------------------|------|-------|------|--------|---------------------------------|

| Analog Input                      |      |       |      |        |                                 |

| Maximum Signal Level              |      |       | ±200 | mV     | Peak value                      |

| ADC                               |      |       |      |        |                                 |

| DC Offset                         |      |       | 10   | mV     |                                 |

| Resolution                        |      | 23    |      | Bit    | Sign bit is included.           |

| Bandwidth (-3dB)                  |      | 1.6   |      | kHz    |                                 |

| On-chip Reference                 |      |       |      | . (    | /1                              |

| Reference Error                   | -18  |       | 18   | mV     |                                 |

| Power Supply Rejection<br>Ratio   |      | 80    |      | dВ     |                                 |

| Temperature Coefficient           |      | 10    | 50   | ppm/°C |                                 |

| Output Voltage                    |      | 1.188 |      | V      |                                 |

| Power Supply                      |      | -/    | ノ)   |        |                                 |

| VDD5                              | 3.0  | 5     | 5.5  | V      |                                 |

| 3.3V LDO (AVCC)                   | ) /  |       |      |        |                                 |

| Voltage                           | 2.8  | 3.3   | 3.5  | V      | VDD5≥4V, I <sub>L33</sub> =16mA |

| Current                           |      |       | 30   | mA     |                                 |

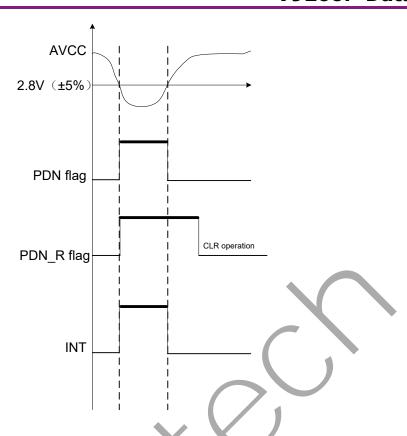

| Power-Down Detection<br>Threshold |      | 2.8   |      | V      | Error: ±5%                      |

| Digital Power Supply (D\          | /CC) |       |      |        |                                 |

|                                   |      |       |      |        | Programmable                    |

| Voltage                           |      | 1.8   |      | V      | Error: ±10%                     |

| Current                           |      |       | 35   | mA     |                                 |

| POR Detection Threshold           |      | 1.45  |      | V      | Error: ±10%                     |

| Pin "CTI"/"CTO"                   |      | 1     | 1    |        | •                               |

| Parameter                                            | Min.  | Тур.   | Max. | Unit   | Remark                      |

|------------------------------------------------------|-------|--------|------|--------|-----------------------------|

|                                                      |       | 3.2768 |      |        |                             |

| Crystal Frequency                                    |       | 6.5536 |      | MHz    |                             |

|                                                      | 30    | 0.000  | 100  | Ω      | For 6.5536-MHz crystal      |

| Equivalent Series Resistance (ESR)                   |       |        |      |        |                             |

| , ,                                                  | 30    |        | 200  | Ω      | For 3.2768-MHz crystal      |

| Phase Error Between Cha                              | nnels |        |      |        |                             |

| PF = 0.8 Capacitive                                  |       | ±0.05  |      | Degree |                             |

| PF = 0.5 Inductive                                   |       | ±0.05  |      | Degree |                             |

| Total Active Energy<br>Metering Error                |       | 0.1    |      | %      | Dynamic Range 5000:1 @ 25°C |

| Total Active Energy<br>Metering Bandwidth            |       | 1.6    |      | kHz    |                             |

| Total Reactive Energy<br>Metering Error              |       | 0.1    |      | %      | Dynamic Range 3000:1 @ 25°C |

| Total Reactive Energy<br>Metering Bandwidth          |       | 1.6    |      | kHz    |                             |

| Fundamental Active<br>Energy Metering Error          |       | 0.1    |      | %      | Dynamic Range 5000:1 @ 25°C |

| Fundamental Active<br>Energy Metering<br>Bandwidth   |       | 65     |      | Hz     |                             |

| Fundamental Reactive<br>Energy Metering Error        |       | 0.1    |      | %      | Dynamic Range 3000:1 @ 25°C |

| Fundamental Reactive<br>Energy Metering<br>Bandwidth |       | 65     |      | Hz     |                             |

| Total VRMS/s Metering<br>Error                       |       | 1      |      | %      | Dynamic Range 1000:1 @ 25°C |

| Total VRMS Metering<br>Bandwidth                     |       | 1.6    |      | kHz    |                             |

| Fundamental VRMS/s<br>Metering Error                 |       | 1      |      | %      | Dynamic Range 5000:1 @ 25°C |

| Fundamental VRMS<br>Metering Bandwidth               |       | 65     |      | Hz     |                             |

| Total IRMS/s Metering Error                          |       | 1      |      | %      | Dynamic Range 1000:1 @ 25°C |

| Total IRMS Metering                                  |       | 1.6    |      | kHz    |                             |

|                                        |        |      |       |      | V9200F Datasileet                                                 |

|----------------------------------------|--------|------|-------|------|-------------------------------------------------------------------|

| Parameter                              | Min.   | Тур. | Max.  | Unit | Remark                                                            |

| Bandwidth                              |        |      |       |      |                                                                   |

| Fundamental IRMS/s<br>Metering Error   |        | 1    |       | %    | Dynamic Range 5000:1 @ 25°C                                       |

| Fundamental IRMS<br>Metering Bandwidth |        | 65   |       | Hz   |                                                                   |

| <b>Current Detection Cycle</b>         | 15     | 25   | 30    | ms   |                                                                   |

| Frequency Measurement                  |        |      |       |      |                                                                   |

| Range                                  | 40     |      | 70    | Hz   |                                                                   |

| Error                                  |        | 0.01 |       | Hz   |                                                                   |

| Logic Output                           | TX/INT |      |       |      |                                                                   |

| Output High Voltage, Voн               | 1.7    |      |       | V    |                                                                   |

| Isource                                |        |      | 8     | mA   | Load of 8-mA current in a short time may not damage the chip, but |

| Output Low Voltage, Vol                |        |      | 0.7   | V    | load of 8-mA for a long time may                                  |

| Isink                                  |        |      | 8     | mA   | damage the chip.                                                  |

| Logic Input                            | RX/A0, | /A1  |       |      | ,                                                                 |

| Input High Voltage, VINH               | 2.0    |      | 3.6   | V    |                                                                   |

| Input Low Voltage, VINL                | -0.3   |      | 0.7   | V    |                                                                   |

| Input Current, I <sub>IN</sub>         |        |      | 1     | μA   |                                                                   |

| Input Capacitance, C <sub>IN</sub>     |        |      | 20    | pF   |                                                                   |

| Baud Rate                              | 1200   | 2400 | 38400 | bps  |                                                                   |

# **Absolute Maximum Ratings**

Operating circumstance exceeding **"Absolute Maximum Ratings"** may cause permanent damage to the device.

| Parameters                         | Min. | Тур. | Max.  | Unit | Description |

|------------------------------------|------|------|-------|------|-------------|

| Power Supply (VDD5)                | -0.3 |      | +8.0  | V    | To ground   |

| Digital Power Supply (DVCC)        | -0.3 |      | +1.98 | V    | To ground   |

| Analog Power Supply (AVCC)         | -0.3 |      | +3.6  | V    | To ground   |

| Analog Input Voltage (IN/IP/UN/UP) | -0.3 |      | +3.3  | V    | To ground   |

| Operating Temperature              | -40  |      | +85   | °C   | )           |

| Storage Temperature                | -55  |      | +150  | °C   |             |

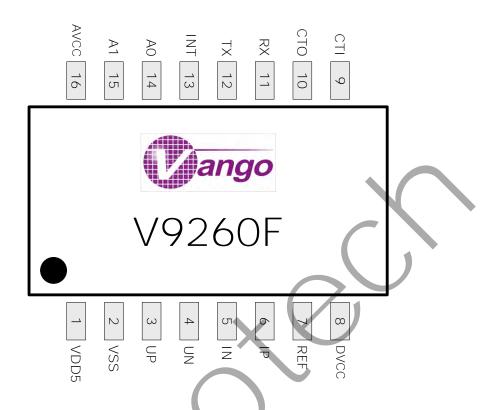

# **Pin Descriptions**

| No. | Mnemonic | Туре         | Description                                                                                                                                                        |

|-----|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDD5     | Power        | 5-V power supply This pin must be decoupled to a $\geq$ 0.1- $\mu$ F capacitor.                                                                                    |

| 2   | VSS      | Ground       | Analog/Digital ground                                                                                                                                              |

| 3   | UP       | Input        | Positive input for Voltage Channel                                                                                                                                 |

| 4   | UN       | Input        | Negative input for Voltage Channel                                                                                                                                 |

| 5   | IN       | Input        | Negative input for Current Channel                                                                                                                                 |

| 6   | IP       | Input        | Positive input for Current Channel                                                                                                                                 |

| 7   | REF      | Input/Output | On-chip reference  This pin must be connected to a 1-µF capacitor, and then grounded.                                                                              |

| 8   | DVCC     | Power        | Digital power output   This pin must be connected to a parallel circuit combined by a $\geq$ 4.7- $\mu$ F capacitor and 0.1- $\mu$ F capacitor, and then grounded. |

|     |          |        | V9200F DataSileet                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Mnemonic | Туре   | Description                                                                                                                                                                                                                                                                                                                                                          |

| 9   | СТІ      | Input  | Connect a 6.5536-MHz crystal around both pins.                                                                                                                                                                                                                                                                                                                       |

| 10  | СТО      | Output | There is fixed load capacitance of 12 pF in the oscillation circuit. The requirement of the crystal oscillator: the load capacitance of crystal oscillator is 12PF, ESR<100 ohm.                                                                                                                                                                                     |

| 11  | RX       | Input  | Receiver data input  Hold low logic for at least 64 ms to reset the chip.  In the Sleep Mode, a low-to-high transition (Holding low and high for at least 250 µs respectively) on this pin can wake up the chip to go to the Current Detection Mode.                                                                                                                 |

| 12  | TX       | Output | Transmitter data output                                                                                                                                                                                                                                                                                                                                              |

| 13  | INT      | Output | Interrupt output, high active  This pin outputs the system control register self-checking interrupt and configuration verification interrupt all the time.  This pin can output the zero-crossing interrupt, current detection interrupt, power-down interrupt, WDT overflow interrupt, or external crystal failure interrupt, when the interrupt output is enabled. |

| 14  | AO       | Input  | Both pins are used to set the chip address for the master MCU to select                                                                                                                                                                                                                                                                                              |

| 15  | A1       | Input  | the slave for communication, when more than one chips are used.                                                                                                                                                                                                                                                                                                      |

| 16  | AVCC     | Output | 3.3-V AVCCLDO output It should be connected to a parallel circuit combined by a $\geqslant$ 4.7- $\mu$ F decouple capacitor and a 0.1- $\mu$ F capacitor, and then connected to the ground.                                                                                                                                                                          |

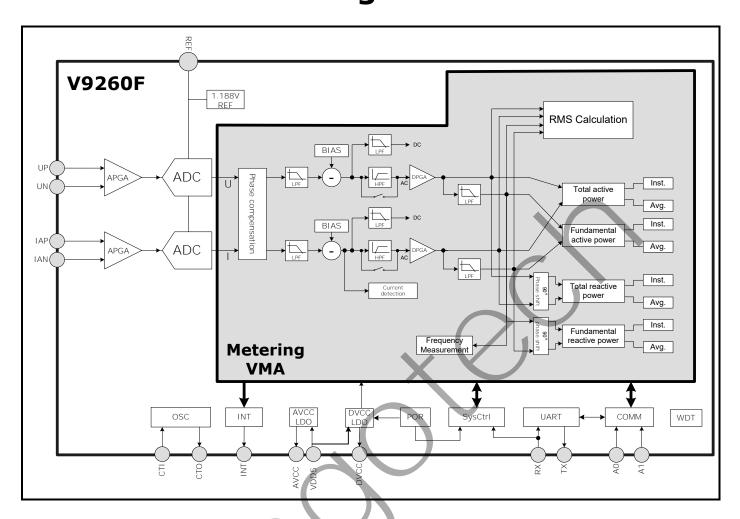

# **Functional Block Diagram**

## **Table of Contents**

| Revisio          | on History                           | 2   |

|------------------|--------------------------------------|-----|

| Featur           | es                                   | 3   |

| Specifi          | ications                             | 4   |

| Absolu           | ıte Maximum Ratings                  | 7   |

| Pin Des          | scriptions                           | 8   |

| Functio          | onal Block Diagram                   | 0   |

| Table o          | of Contents                          | 1   |

| Figure           | List                                 | 3   |

| Table L          | List                                 | .)4 |

| 1. R             | Reset                                | ,6  |

| 1.1.             | Power-On Reset (POR)                 |     |

| 1.2.             | RX Reset                             |     |

| 1.3.             |                                      | 7   |

| 1.4.             | . WDT Overflow Reset                 | 8   |

| 1.5.             | 9                                    |     |

| 2. C             | Clock                                |     |

| 2.1.             |                                      |     |

| 2.2.             |                                      |     |

| 2.3.             |                                      | 14  |

| 2.4.             |                                      |     |

|                  | Operation Mode                       |     |

| 3.1.             |                                      | 20  |

| 3.2.             | . Sleep Mode  Current Detection Mode |     |

| 3.4.             |                                      |     |

|                  |                                      |     |

| <b>4. P</b>      | Power Supply Monitoring Circuit      |     |

| 4.1.<br>4.2.     | 3                                    |     |

| 4.3.             |                                      |     |

|                  | Bandgap Circuit                      |     |

|                  |                                      |     |

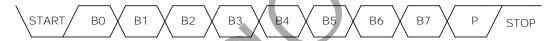

| <b>6. U</b> 6.1. | JART Interface  Data Byte            |     |

| 6.2.             | •                                    |     |

| 6.3.             | 9                                    |     |

|                  | 6.3.1. Write Operation               |     |

|                  | 6.3.2. Read Operation                |     |

|    | 6    | .3.3. Broadcast Communication                   | 37  |

|----|------|-------------------------------------------------|-----|

| 7. | RM   | 1S & Power Measurement                          | 39  |

|    | 7.1. | Metering Clock (MEACLK)                         | 39  |

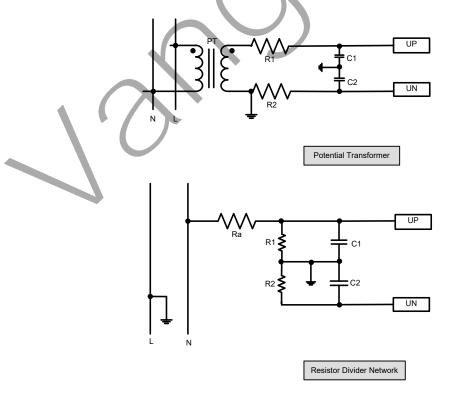

|    | 7.2. | Analog Input                                    | 39  |

|    | 7.3. | Analog-to-Digital Conversion                    | 41  |

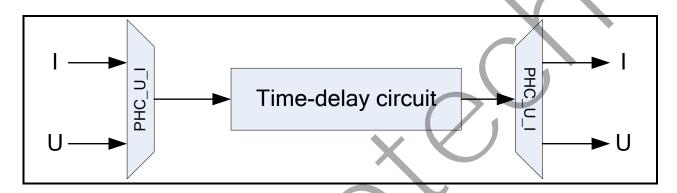

|    | 7.4. | Phase Compensation                              | 42  |

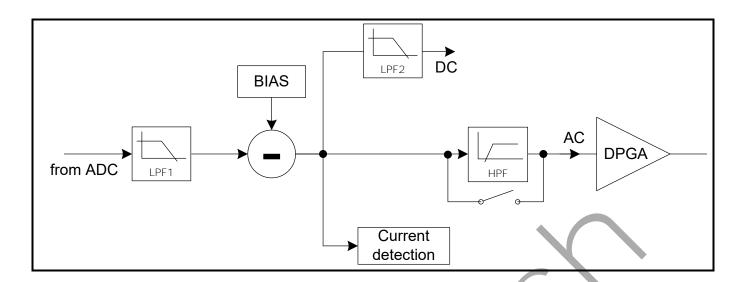

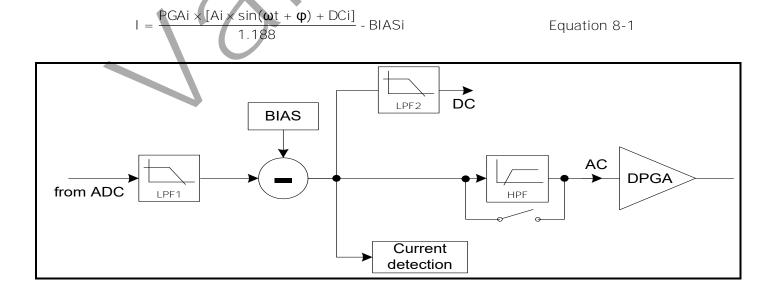

|    | 7.5. | Digital Input and DC Removement                 | 44  |

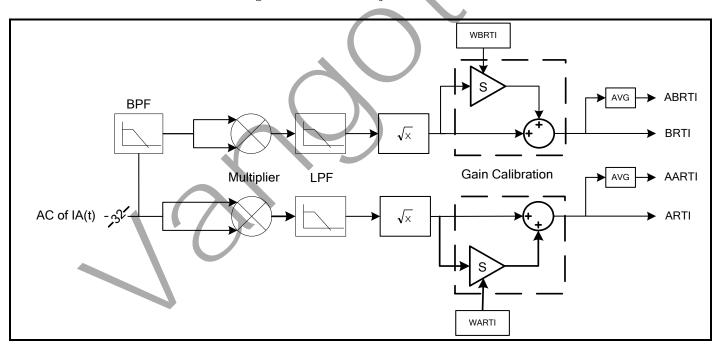

|    | 7.6. | RMS Calculation                                 | 45  |

|    | 7.7. | Power Calculation                               | 47  |

|    | 7.8. | Line Frequency Measurement                      | 49  |

|    | 7.9. | Calibration                                     | 50  |

|    | 7    | 7.9.1. Registers for Meter Calibration          |     |

|    | 7    | 7.9.2. Equations for Calibration                | 51  |

|    | 7    | '.9.3. Calibration Steps                        | 53  |

| 8. | Int  | terrupt                                         | 55  |

|    | 8.1. | System Control Register Self-Checking Interrupt |     |

|    | 8.2. | Configuration Verification Interrupt            | 56  |

|    | 8.3. |                                                 |     |

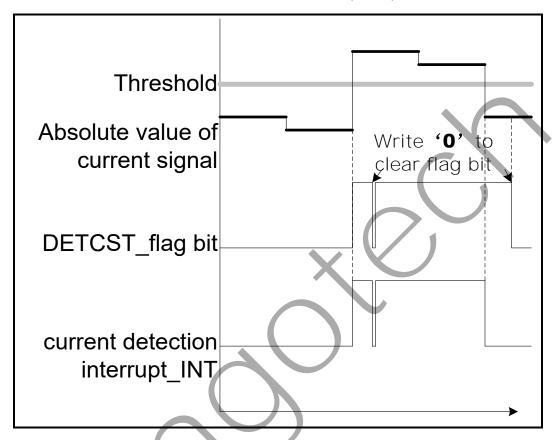

|    | 8.4. | Current Detection Interrupt                     | 58  |

|    | 8.5. | Registers                                       | 59  |

| 9. | Re   | gisters                                         |     |

| -  | 9.1. | Analog Control Registers                        | 63  |

|    | 9.2. | System Control Register                         |     |

|    | 9.3. | Metering Control Registers                      | 72  |

|    | 9.4. | Data Registers                                  |     |

|    | 9.5. | Registers for Calibration                       |     |

|    | 9.6. | Checksum Register                               |     |

|    | •    | Allina Dimanatana                               | 0.4 |

# **Figure List**

| Figure 1-1 Timing of POR                                                            | 6  |

|-------------------------------------------------------------------------------------|----|

| Figure 1-2 Timing of RX Reset                                                       | 7  |

| Figure 1-3 Timing of Global Software Reset                                          | 8  |

| Figure 1-4 WDT Overflow Reset (Reset interval is set to 32 s.)                      | 9  |

| Figure 2-1 Clock Generation                                                         | 12 |

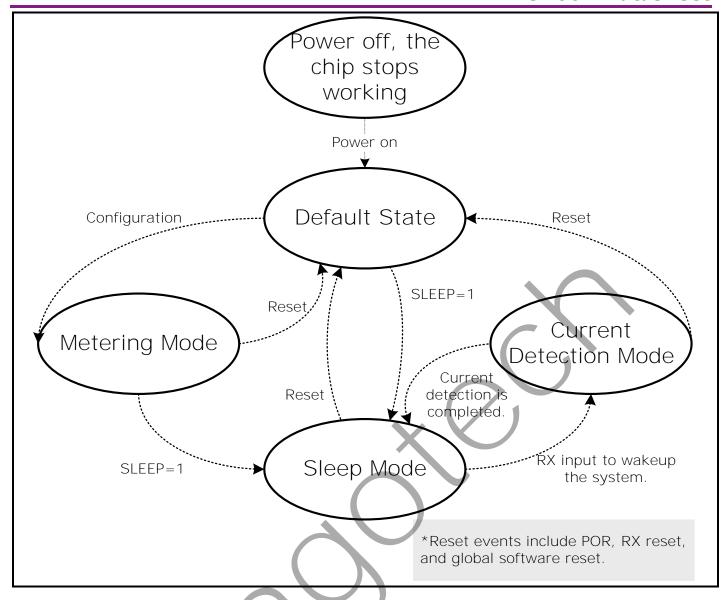

| Figure 3-1 Operating Modes                                                          | 20 |

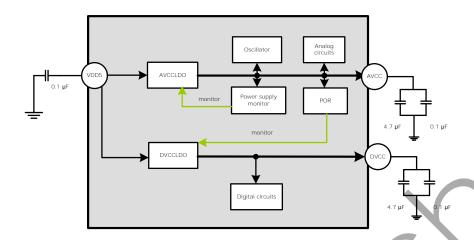

| Figure 4-1 Power Supply Architecture                                                |    |

| Figure 4-2 Power-Down Interrupt                                                     | 28 |

| Figure 6-1 Structure of an 11-Bit Data Byte                                         | 32 |

| Figure 6-2 Command Frame for Read/Write/Broadcast Operation                         | 33 |

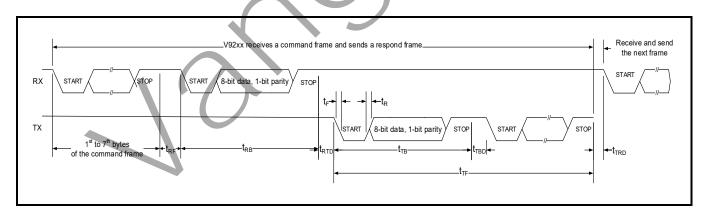

| Figure 6-3 Timing of UART Communication                                             | 34 |

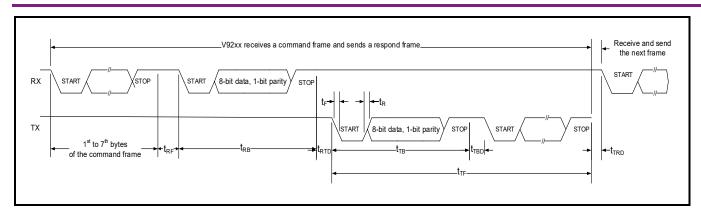

| Figure 7-1 Signal Processing in Specific Metering Architecture                      | 39 |

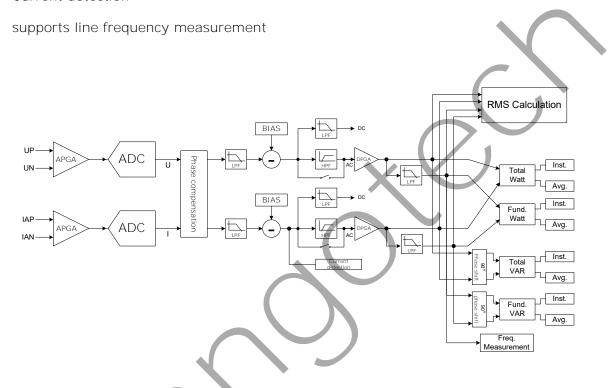

| Figure 7-2 Analog Input of Current Channels                                         | 40 |

| Figure 7-3 Analog Input of Voltage Channels                                         | 40 |

| Figure 7-4 Phase Compensation                                                       | 43 |

| Figure 7-5 Digital Input and DC Removement (Current Signal is Taken as an Example.) | 44 |

| Figure 7-6 Total/Fundamental RMS Calculation                                        | 46 |

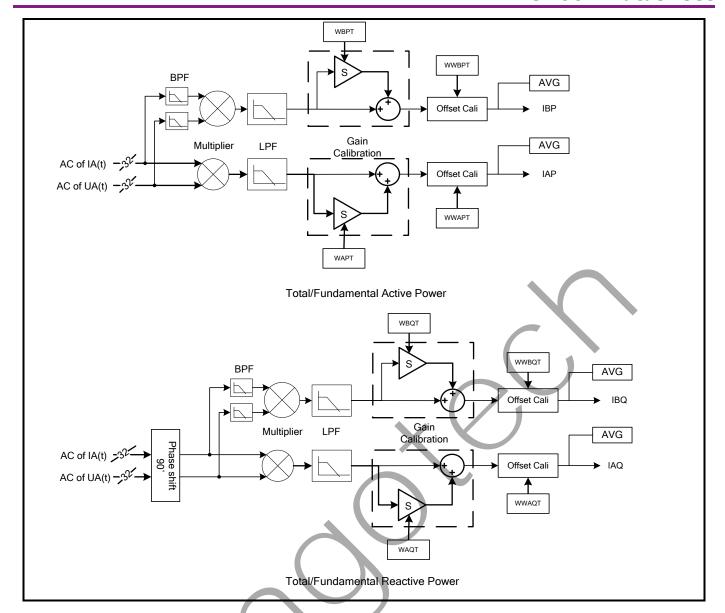

| Figure 7-7 Active/Reactive Power Calculation                                        | 48 |

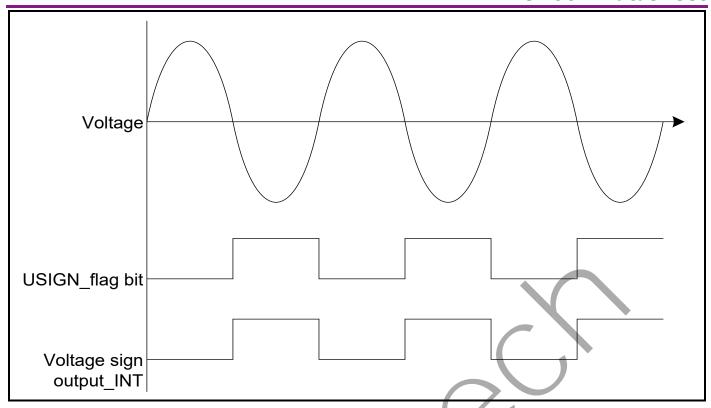

| Figure 8-1 Zero-Crossing Interrupt                                                  |    |

| Figure 8-2 Signal Processing for Current Detection                                  | 58 |

| Figure 8-3 Current Detection Interrupt                                              | 50 |

# **Table List**

| Table 1-1 Theoretical Reset Interval and Recommended Interval to Feed Dog              | 9  |

|----------------------------------------------------------------------------------------|----|

| Table 1-2 Reset Related Registers                                                      | 10 |

| Table 2-1 Clock Generation Related Registers                                           | 15 |

| Table 3-1 States of Functional Units in Default State                                  | 19 |

| Table 3-2 States of Functional Units in Metering Mode                                  | 21 |

| Table 3-3 States of Functional Units in Sleep Mode                                     | 22 |

| Table 3-4 States of Functional Units in Current Detection Mode                         | 23 |

| Table 3-5 Factors Affecting Power Dissipation                                          | 24 |

| Table 3-6 Effects on ADCs Power Dissipation                                            | 25 |

| Table 3-7 Effect on Vango Metering Architecture Power Dissipation                      | 25 |

| Table 3-8 Power Dissipation in Each Operating Mode                                     |    |

| Table 4-1 DVCCLDO Output Voltage Adjustment                                            | 28 |

| Table 5-1 Configuration for Bandgap Circuit                                            | 30 |

| Table 6-1 Baud Rate Configuration                                                      | 32 |

| Table 6-2 UART Communication Timing Parameters                                         | 34 |

| Table 6-3 Structure of Data Byte (B7:B0) From Master MCU to V9260F on Write Operation  | 35 |

| Table 6-4 Structure of Data Byte (B7:B0) From V9260F to Master MCU on Write Operation  | 35 |

| Table 6-5 Structure of Data Byte (B7:B0) From Master MCU to V9260F on Read Operation.  | 36 |

| Table 6-6 Structure of Data Byte (B7:B0) From V9260F to Master MCU on Read Operation.  | 36 |

| Table 6-7 Structure of Data Byte (B7:B0) From Master MCU to V9260F on Broadcast Operat |    |

|                                                                                        |    |

| Table 7-1 Analog PGA Configuration                                                     |    |

| Table 7-2 Enable/Disable ADCs of Each Channel                                          |    |

| Table 7-3 Configuring ADCCLK                                                           |    |

| Table 7-4 Registers for phase compensation                                             | 42 |

| Table 7-5 Resolution and correction range at different frequencies                     | 43 |

| Table 7-6 Enable/Disable Digital Inputs                                                | 44 |

| Table 7-7 DPGA Gain Selection for Digital Signals                                      | 45 |

| Table 7-8 Bandpass Filter Parameters                                                   | 50 |

| Table 7-9 Registers for Meter Calibration                                              | 50 |

| Table 8-1 Registers for Configuration Verification56                                       |

|--------------------------------------------------------------------------------------------|

| Table 8-2 Interrupt Output Enable Bits59                                                   |

| Table 8-3 Interrupt Flag Bits60                                                            |

| Table 9-1 Analog Control Register 0 (ANCtrl0, 0x0185)63                                    |

| Table 9-2 Analog Control Register 2 (ANCtrl2, 0x0187)66                                    |

| Table 9-3 System Control Register (0x0180, SysCtrl)68                                      |

| Table 9-4 Metering Control Register 0 (0x0183, MTPARA0)73                                  |

| Table 9-5 Metering Control Register 1 (0x0184, MTPARA1)74                                  |

| Table 9-6 Registers for DC Component (R/W)76                                               |

| Table 9-7 Registers for Line Frequency (R)76                                               |

| Table 9-8 Registers for RMS Values of Total/Fundamental Signals (R/W)77                    |

| Table 9-9 Total/Fundamental Active/Reactive Power Registers (R/W)79                        |

| Table 9-10 Registers for Presetting Bias for Direct Current/Voltage81                      |

| Table 9-11 Registers for Calibrating Voltage/Current RMS (R/W)81                           |

| Table 9-12 Registers for Calibrating Active/Reactive Power (R/W)81                         |

| Table 9-13 Threshold Register82                                                            |

| Table 9-14 Register for Bandpass Filter Coefficient Configuration (0x0125, BPFPARA, R/W)83 |

| Table 9-15 Checksum Register (0x0133, CKSUM, R/W)83                                        |

### 1.Reset

In V9260F, the chip will be reset to the Default State, when a POR reset, RX reset, or global software reset occurs; and the UART serial interface will be reset when the WDT overflow event occurs.

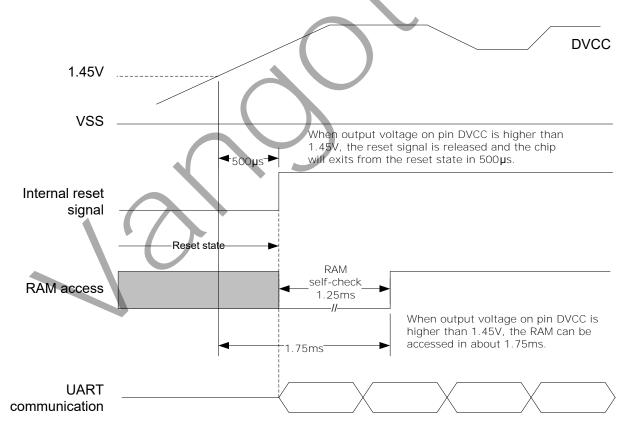

## 1.1. Power-On Reset (POR)

In V9260F, the internal power-on reset circuit supervises the output voltage on the pin "**DVCC"** all the time. When the output voltage is lower than 1.45 V, the reset signal will be generated and forces the chip into the reset state. When the output voltage is higher than 1.45 V, the reset signal will be released and the chip will go to the Default State in 500  $\mu$ s.

When a POR event occurs, the bit "RSTSRC" (bit[26:24] of SysCtrl, 0x0180) will be reset to "0b001".

In the reset state, the master MCU and the Vango metering architecture cannot access RAM. When the chip exits from the reset state, RAM will implement the self-checking in about 1.25 ms. If there is no error occurring, RAM can be accessed.

In the reset state, the UART serial interface is idle. The interface starts to run immediately once the chip exits from the reset state.

Figure 1-1 Timing of POR

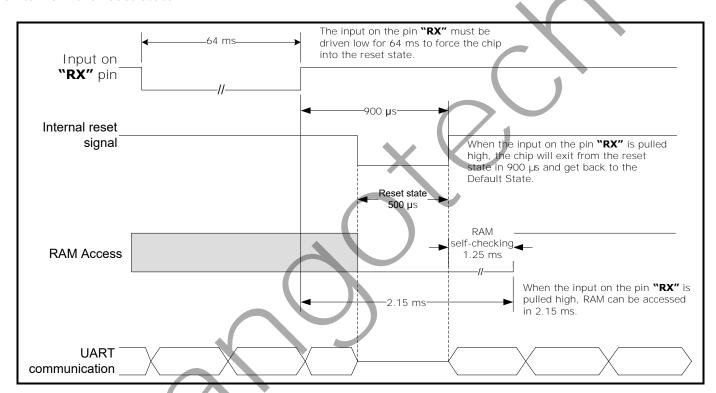

#### 1.2. RX Reset

The input on the pin "RX" must be driven low for at least 64 ms to force the chip into the reset state. Pull the pin "RX" to the logic high, and 900  $\mu$ s later the chip will exit from the reset state and get back to the Default State.

When a RX reset occurs, the bit "RSTSRC" (bit[26:24] of SysCtrl, 0x0180) will be reset to "0b011".

In the reset state, the master MCU and the Vango metering architecture cannot access RAM. When the chip exits from the reset state, RAM will implement the self-checking in about 1.25 ms. If there is no error occurring, RAM can be accessed.

In the reset state, the UART serial interface is idle. The interface starts to run immediately once the chip exits from the reset state.

**Figure 1-2 Timing of RX Reset**

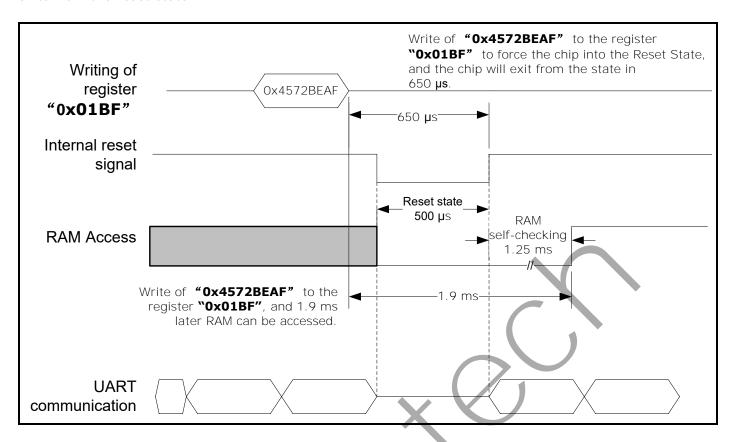

## 1.3. Global Software Reset

In V9260F, writing of "0x4572BEAF" in the register "SFTRST" (0x01BF) can force the chip into the reset state, and the chip will exit and get back to the Default State in 650  $\mu s$ .

When a global software reset occurs, the bit "RSTSRC" (bit[26: 24] of SysCtrl, 0x0180) will be reset to "0b100".

In the reset state, the master MCU and the Vango metering architecture cannot access RAM. When the chip exits from the reset state, RAM will implement the self-checking in about 1.25 ms. If there is no error occurring, RAM can be accessed.

In the reset state, the UART serial interface is idle. The interface starts to run immediately once the chip

exits from the reset state.

Figure 1-3 Timing of Global Software Reset

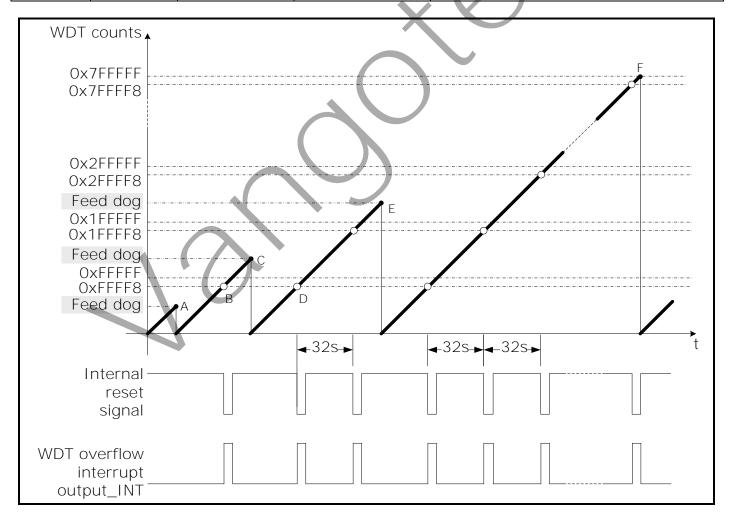

### 1.4. WDT Overflow Reset

V9260F integrates a 23-bit watchdog timer (WDT) counting pulses of the 32-kHz RC clock (CLK3). The 32-kHz RC oscillator works all the time when the chip is powered on, so WDT keeps on counting the pulses. If WDT is not cleared at the preset interval (Feed dog), the WDT counts will overflow, a WDT overflow reset signal will be generated, and the baud rate of UART interface will be reset to 2400 bps.

#### Note:

Please note that the baud rate of UART interface will be reset to 2400 bps when a WDT overflow event occurs, but the configuration of bits **"CKUDIV"** (bit[4:2] of SysCtrl, 0x0180) holds on.

The WDT counts will be cleared when a POR reset event occurs, the pin "RX" receives a correct command frame for the write, read, or broadcast operation, or the chip is woken up from the Sleep Mode.

Users can configure the interval (T) for the WDT overflow reset via "bit[17:15]" of register "MTPARAO" (0x0183) to lower the power dissipation or speed up the debugging. The reset interval is affected by the "CLK3" frequency that has a drift of  $\pm 50\%$ . In practice, 32768 Hz is taken as the "CLK3" frequency for the interval calculation, but to protect the UART serial interface from being reset, it is recommended to feed dog before at an interval of  $\frac{T}{2}$  to avoid the WDT overflow reset.

Table 1-1 Theoretical Reset Interval and Recommended Interval to Feed Dog

| Register | Bit        | Configuration | Reset Interval (T) | Recommended Interval to Feed Dog $(\frac{1}{2})$ |

|----------|------------|---------------|--------------------|--------------------------------------------------|

|          |            | 000           | 2 s                | 1 s                                              |

|          |            | 001           | 4 s                | 2 s                                              |

|          |            | 010           | 8 s                | 4 s                                              |

| 0x0183   | Bit[17:15] | 011           | 16 s               | 8 s                                              |

| MTPARA0  | WDT        | 100           | 32 s               | 16 s                                             |

|          |            | 101           | 64 s               | 32 s                                             |

|          |            | 110           | 128 s              | 64 s                                             |

|          |            | 111           | 256 s              | 128 s                                            |

Figure 1-4 WDT Overflow Reset (Reset interval is set to 32 s.)

As shown in

Figure 1-4,

If the counts are cleared before the timer counts to "OxFFFF8" (As "A" in

- Figure 1-4), WDT will count from '0' again. "16 s" is recommended as the interval to feed dog.

- If WDT keeps on counting over "OxFFFF8", a reset signal will be generated and hold for 8 CLK3 cycles till WDT counts to "OxFFFFF". After the reset, WDT will continue to count, and then,

WDT will count from **'0'** again when the counts are cleared before the timer counts to **"0x1FFFF8"** (As **"C"** in

- ✓ Figure 1-4).

- ✓ WDT will keep on counting until it is cleared or it counts to "0x7FFFFF" and then are cleared automatically. The UART interface will be reset every 32 s until the counts are cleared.

Modify the reset interval, and it will not be activated until the dog is fed.

When WDT overflow reset occurs, the bit "RSTSRC" (bit[26:24] of SysCtrl, 0x0180) is reset to "0b000", and an interrupt is triggered. When the WDT interrupt output is enabled (IEWDT, bit5 of MTPARAO, 0x0183, is set to '1'), the pin "INT" will output high logic for 8 CLK3 cycles, and then low logic automatically.

## 1.5. Registers

**Table 1-2 Reset Related Registers**

|          | Reset Relate | a regional                                                                                                                                                             |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register | Bit          | Description                                                                                                                                                            |

|          |              | Flag bits to indicate the reset source                                                                                                                                 |

|          |              | Bit26 Bit25 Bit24 Description                                                                                                                                          |

| 0x0180   | Bit[26: 24]  | 0 0 1 A POR event occurred.                                                                                                                                            |

| SysCtrl  | RSTSRC       | 0 0 0 A WDT overflow event occurred.                                                                                                                                   |

|          |              | 0 1 1 An RX reset event occurred.                                                                                                                                      |

| <b>*</b> |              | 0 1 0 Reserved                                                                                                                                                         |

|          |              | 1 0 0 A global software reset occurred.                                                                                                                                |

|          |              | To set the interval for WDT overflow reset (T)                                                                                                                         |

|          |              | "T" is calculated via equation $T = \frac{2^{WDT}}{f_{CLK3}}$ , of which,                                                                                              |

| 0x0183   | Bit[17:15]   | • WDT is the value of bit[17:15].                                                                                                                                      |

| MTPARAO  | WDT          | 000: 16; 001: 17; 010: 18; 011: 19; 100: 20; 101: 21; 110: 22; 111: 23.                                                                                                |

|          |              | • f <sub>CLK3</sub> is the actual frequency of "CLK3". In practice, 32768 Hz is taken to calculate the interval (T). But there is an error of $\pm 50\%$ of the "CLK3" |

| della.   |              | frequency, so it is recommended to feed dog at an interval of $\frac{T}{2}$ to prevent                                                                                 |

| Register                                        | Bit           | Description                                                                                                        |  |  |  |

|-------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                 |               | the baud rate of UART serial interface from being reset by the WDT overflow.                                       |  |  |  |

|                                                 | Bit5<br>IEWDT | To enable WDT overflow interrupt output  1: Enable  0: Mask                                                        |  |  |  |

| Ox01BF, SFTRST  Software Reset Control Register |               | Readable and writable, in the form of 32-bit 2' complement  Write "0x4572BEAF" to the register to reset the system |  |  |  |

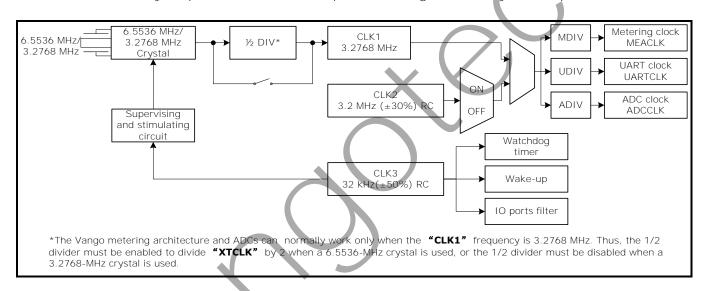

## 2.Clock

The on-chip RC oscillator circuits and the crystal oscillation circuit provide clocks for V9260F:

- On-chip crystal oscillation circuit: An external 6.5536-MHz or 3.2768-MHz crystal connects to the pins "CTI" and "CTO" to generate the clock (CLK1) that works as the clock source for the Vango metering architecture, ADCs, and UART serial interface. After a POR, RX reset, or global software reset occurs, this oscillation circuit starts to run.

- On-chip 3.2-MHz (±30%) RC oscillator generates the clock (CLK2) that works as an optional clock source for the Vango metering architecture, ADCs, and UART serial interface. This circuit can be disabled. After a POR, RX reset, or global software reset occurs, this circuit stops running.

- On-chip 32-kHz (±50%) RC oscillator generates the clock (CLK3) that works as the clock source for the watchdog timer, wake-up circuit, internal crystal supervising and stimulating circuit, and the filters for some key IO ports. This circuit keeps on working until the system is powered off.

Figure 2-1 Clock Generation

## 2.1. Crystal Oscillation Circuit

In the on-chip crystal oscillation circuit, there is fixed load capacitance (CL) of 12 pF. In applications, users can adjust the capacitance via configuring bits "XCSEL<1:0>" (bit[17:16] of ANCtrl2, 0x0187) or connecting additional capacitors around pins "CTI" and "CTO" to adjust the oscillation frequency.

When powered on, the crystal oscillation circuit starts to run to generate a clock, "XTCLK", to be the source of clock "CLK1". The "CLK1" frequency is divided by different clock scalars to generate clocks for the Vango metering architecture (MEACLK), ADCs (ADCCLK), and UART interface (UARTCLK). The master MCU can configure the bit "XTALPD" (bit20 of ANCtrl0, 0x0185) to disable the oscillation circuit. When the oscillation circuit stops working, the on-chip 3.2-MHz (The deviation is within ±30% from chip to chip for mass production. The temperature deviation from -40~85 degree for each specific chip is less than 3%.) RC oscillator will start to run automatically to generate clock "CLK2" to replace "CLK1" to provide clock pulses for the Vango metering architecture, ADCs, and UART interface. However, please be noted that the "CLK2" frequency is not accurate enough for the UART communication.

Both 3.2768-MHz and 6.5536-MHz crystals can be connected around the pins "CTI" and "CTO". Thus, the "XTCLK" frequency can be 3.2768 MHz or 6.5536 MHz. However, the Vango metering architecture and ADCs can work normally only when the "CLK1" frequency is 3.2768 MHz. Thus, the 1/2 divider must be enabled when a 6.5536-MHz crystal is used; otherwise, it must be disabled. Users can enable or disable this divider via configuring the bit "XTAL3P2M" (bit19 of ANCtIr0, 0x0185).

Please be noted that the 1/2 divider is enabled after a POR, RX reset, or global software reset occurs. Thus, the UART interface will communicate at a half of the expected baud rate when the 3.2768-MHz crystal is used. Users must disable the divider via the bit "XTAL3P2M" (bit19 of ANCtrl0, 0x0185).

Users can adjust the clock frequency for ADCs and metering architecture via bits "ADCCLKSEL<1:0>" (bit[17:16] of ANCtrl0, 0x0185) and "CKMDIV" (bit1 of SysCtrl, 0x0180), and the baud rate for the UART communication via bits "CKUDIV" (bit[4:2] of SysCtrl, 0x0180).

The typical power dissipation of the crystal oscillation circuit is 130  $\mu$ A. When a 3.2768-MHz crystal is used, users must set the bit "XTALLP" to '1' to lower the power dissipation to a half. When a 6.5536-MHz crystal is used, setting this bit has no effect on the power dissipation of this circuit. When a crystal of higher than 60- $\Omega$  ESR (Equivalent Serial Resistance) is used, users must set the bit "XRSEL<0>" (bit18 of ANCtrl2, 0x0187) to '1' to improve the driving ability of the oscillation circuit to ensure the crystal to work, which needs additional 55- $\mu$ A load current.

In the Metering Mode, some errors can stop the oscillation circuit. Thus, an internal supervising and stimulating circuit, which is sourced by "CLK3", is designed to monitor the crystal all the time. When the crystal stops oscillating, this circuit will generate a 1-ms wide pulse every second to stimulate the crystal to restore oscillating. The stimulating function of this circuit is disabled by default. Users can set the bit "XRSTEN" (bit21 of ANCtrl0, 0x0185) to '1' to enable this function.

In the Sleep Mode, this crystal oscillation circuit stops working, and it will not get back to work automatically even though the system is woken up from the Sleep Mode to get to the Current Detection Mode.

When the crystal stops working, an interrupt signal is generated and the flag bit "HSEFAIL" (bit27 of SysCtrl, 0x0180) is set to '1', which will be cleared when the crystal restores to work. If the external crystal failure interrupt output is enabled (IEHSE, bit4 of MTPARAO, is set to '1'), the pin "INT" will output high logic and hold the state till the crystal works again.

Please be noted that the "CLK2" frequency is not accurate enough for the UART communication, so the master MCU cannot read the actual state of the flag bit "HSEFAIL".

### 2.2. 3.2-MHz RC Oscillator

In V9260F, an on-chip 3.2-MHz RC oscillator is designed to generate a 3.2768-MHz (The deviation is within  $\pm 30\%$  from chip to chip for mass production. The temperature deviation from -40~85 degree for each specific chip is less than 3%.) clock, "CLK2", to work as an optional clock source for the Vango metering architecture, ADCs, and UART serial interface. But the "CLK2" frequency is not accurate enough for the UART communication. In the Metering Mode, this circuit will start to run automatically when the crystal stops working, and it will stop running automatically when the crystal restores to work.

After a POR, RX reset, or global software reset occurs, this circuit stops running. To enable this circuit, it is mandatory to enable the Bandgap and global biasing current circuits firstly which provides the biasing current and reference voltage for the 3.2-MHz RC oscillator.

In the Sleep Mode, this circuit stops running, and it will get back to work automatically when the chip is woken up from the Sleep Mode to go to the Current Detection Mode.

## 2.3. 32-kHz RC Oscillator

The on-chip 32-kHz RC oscillator can generate a 32-kHz ( $\pm 50\%$ ) RC clock (CLK3) to drive the watchdog timer, wake-up circuit, internal crystal supervising and stimulating circuit, and the filters for some key IO ports. This oscillator cannot be disabled until the system is powered off.

## 2.4. Registers

Table 2-1 Clock Generation Related Registers

| Register          | Bit              | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Bit29<br>PDRCCLK | N/A     | Clear this bit to enable the 3.2-MHz RC Clock. It is mandatory to enable the Bandgap circuit and biasing circuit firstly. The value of the bit is uncertain when the system is reset.                                                                                                                                                                                                                                                                                                                                                                  |

|                   |                  |         | In the Sleep Mode, this bit is set to <b>'1'</b> automatically. In the Current Detection Mode, this bit is cleared automatically.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |                  |         | In the Metering Mode, when the chip operates with full functions, it is recommended to disable this circuit (Set the bit to '1').                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ox0185<br>ANCtrIO | Bit28<br>BIASPDN | 0       | Set this bit to <b>'1'</b> to enable the biasing circuit to provide the global biasing current for ADCs and the 3.2-MHz RC oscillator. Therefore, in the Metering Mode, when the chip operates with full functions, this bit must be set to <b>'1'</b> before enabling ADCs and the 3.2-MHz RC oscillator. By default the biasing circuit is disabled.  In the Sleep Mode, this bit is cleared automatically. In the Current Detection Mode, this bit is set to <b>'1'</b> automatically.  In the Metering Mode, this biasing circuit must be enabled. |

|                   | Bit27<br>BGPPDN  | 0       | Set this bit to '1' to enable the Bandgap circuit to provide ADCs and the 3.2-MHz RC oscillator with the reference voltage and biasing voltage. Therefore, in the Metering Mode, when the chip operates with full functions, this bit must be set to '1' before enabling ADCs and the 3.2-MHz RC oscillator. By default the Bandgap circuit is disabled.  In the Sleep Mode, this bit is cleared automatically. In the Current Detection Mode, this bit is set to '1' automatically.  In the Metering Mode, this Bandgap circuit must be enabled.      |

|                   | Bit21<br>XRSTEN  | 0       | Set this bit to <b>'1'</b> to enable the function of stimulating the external crystal when it stops running. By default this function is disabled.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   |                  |         | In the Metering Mode, when the chip operates with full functions, it is recommended to enable this function for the best performance.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | v9260F Datasneet         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------|--------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Register | Bit                      | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|          | Bit20<br>XTALPD          | 0       | Set this bit to <b>'1'</b> to disable the crystal oscillation circuit. By default this circuit is enabled. In the Metering Mode, when the chip operates with full functions, this bit will be set to <b>'1'</b> when the external crystal stops running, but it will be cleared automatically when the crystal restores running.  Both in the Sleep Mode and in the Current Detection Mode, this bit is set to <b>'1'</b> automatically.                                                                                            |  |

|          | Bit19<br>XTAL3P2M        | 0       | When a 3.2768-MHz external crystal is used, this bit must be set to <b>'1'</b> to disable the 1/2 divider in the crystal oscillation circuit.  When a 6.5536-MHz crystal is used, this bit must be cleared to enable the 1/2 divider.                                                                                                                                                                                                                                                                                               |  |

|          | Bit18<br>XTALLP          | 0       | When a 3.2768-MHz crystal is used, it is mandatory to set this bit to <b>'1'</b> to lower the power dissipation of the crystal oscillation circuit to a half.  When a 6.5536-MHz crystal is used, this bit must hold its default value.                                                                                                                                                                                                                                                                                             |  |

|          | Bit[17:16] ADCLKSEL<1:0> |         | To select the sampling frequency of the oversampling ADC (ADC clock, ADCCLK). The sampling frequency of ADCs must be a quarter or one eighth of the metering clock (MEACLK) frequency when the chip operates with full functions in the Metering Mode.  O0: 819.2 kHz  O1: 409.6 kHz  10: 204.8 kHz  In the Current Detection Mode, these bits must be set to "Ob10" to lower the power dissipation.  When the chip operates with full functions in the Metering Mode, their default values are recommended to be used for the best |  |

| Bit                      | Default                                 | <b>Description</b> To adjust the 3.2-MHz RC clock cycle                                                                                                                                                                                         |

|--------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                         | To adjust the 3.2-MHz RC clock cycle                                                                                                                                                                                                            |

|                          |                                         |                                                                                                                                                                                                                                                 |

|                          |                                         | The resolution is 1% per LSB. When these bits are in their default state, no adjustment is applied.                                                                                                                                             |

| Bit[29: 24]  RCTRIM<5:0> | 0                                       | From "0b000000" to "0b100000", the RC clock cycle is decreased by 1% per LSB; from "0b100001" to "0b111111", the RC clock cycle is increased by 1% per LSB.                                                                                     |

|                          |                                         | When the chip operates with full functions in the Metering Mode, it is recommended to hold their default values for the best performance.                                                                                                       |

| Bit19                    |                                         | To adjust the negative resistance of the crystal oscillator                                                                                                                                                                                     |

| XRSEL<1>                 | 0                                       | It is not recommended to set this bit to '1', which will lead to additional 18-µA load current.                                                                                                                                                 |

| Bit18<br>XRSEL<0>        | 0                                       | To adjust the negative resistance of the crystal oscillator When the equivalent series resistance of the crystal is higher than 60 $\Omega$ , it is recommended to set this bit to '1', which will lead to additional 55- $\mu A$ load current. |

| Bit[17:16]<br>XCSEL<1:0> | 0                                       | To adjust the load capacitance of the crystal oscillator  By default the load capacitance is 12 pF.  00: No adjustment  01: +2 pF  10: +4 pF  11: +6 pF                                                                                         |

| Bit4<br>IEHSE            | 0                                       | To enable external crystal failure interrupt output  1: Enable  0: Mask                                                                                                                                                                         |

|                          | Bit18  XRSEL<0>  Bit[17:16]  XCSEL<1:0> | Bit18 XRSEL<0>  Bit[17:16] XCSEL<1:0>  Ditable 10                                                                                                                                                                                               |

| V9200F Datasileet |                    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register          | Bit                | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   |                    |         | External crystal failure interrupt flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x0180<br>SysCtrl | Bit27<br>HSEFAIL   | 0       | When the external crystal stops running, this bit will be set bit and hold the state till the crystal starts to oscillate again.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                    |         | When the crystal stops running, the UART serial interface is sourced by the 3.2-MHz RC clock (CLK2), which is not accurate enough for the UART communication, so the master MCU cannot read the value of this bit to detect the state of the crystal. In this circumstance, users should enable the external crystal failure interrupt output on the pin "INT" to help to detect the state of the crystal.                                                                                                                                                                                          |

|                   | Bit[4:2]<br>CKUDIV | 1       | To set the baud rate for the UART communication, in unit of bps. 000: 1200; 001: 2400; 010: 4800; 011: 9600; 100: 19200; 101: 38400; 110/111: 1200.  Note: When a 3.2768-MHz crystal is used, after a power-on reset (POR), RX reset, or global software reset occurs, the actual baud rate is a half of the desired baud rate. In this case, users must set the bit "XTAL3P2M" (bit19 of ANCtrl0, 0x0185) to '1' to disable the 1/2 divider to generate 3.2768-MHz CLK1 to source the UART interface. After the WDT overflow reset, the baud rate is reset to 2400 bps, but these bits holds their |

|                   | Bit1<br>CKMDIV     | 0       | To select the clock frequency for the Vango metering architecture (MEACLK)  1: 819.2 kHz  0: 3.2768 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | BitO<br>SLEEP      | 0       | Set this bit to '1' to disable "CLK1" and "CLK2" and force the system to enter the Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## 3. Operation Mode

When V9260F is powered off, the chip stops working and it will go to the Default State when being powered on.

When the chip is working, it can be reset to the Default State when a POR, RX reset, or global software reset occurs. Table 3-1 lists the states of functional units in V9260F in the Default State.

In the Default State, the typical load current is 500  $\mu$ A. Some easy configurations can drive the chip to work in the Metering Mode or Sleep Mode.

Table 3-1 States of Functional Units in Default State

| Functional Unit                 | State                                                                                                                                                                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM                             | Cleared to all zeros                                                                                                                                                                                                                                         |

| Crystal oscillation circuit     | Enabled                                                                                                                                                                                                                                                      |

| 3.2-MHz RC oscillator           | Disabled                                                                                                                                                                                                                                                     |

| 32-kHz RC oscillator            | Enabled                                                                                                                                                                                                                                                      |

| Bandgap circuit                 | Disabled                                                                                                                                                                                                                                                     |

| Biasing circuit                 | Disabled                                                                                                                                                                                                                                                     |

| Power supply monitoring circuit | Enabled                                                                                                                                                                                                                                                      |

| POR circuit                     | Enabled                                                                                                                                                                                                                                                      |

| LDO                             | Enabled                                                                                                                                                                                                                                                      |

| ADC                             | Disabled                                                                                                                                                                                                                                                     |

| Vango metering architecture     | Enabled, but for configuration verification only                                                                                                                                                                                                             |

| Interrupt management circuits   | Enabled. Output system control register self-checking interrupt and configuration verification interrupt only                                                                                                                                                |

| UART serial interface           | Enabled. When a 3.2768-MHz crystal is used, the actual baud rate will be a half of desired baud rate. Users must set the "XTAL3P2M" bit (Bit19, 0X0185,ANCtrl0) to '1' to disable the 1/2 divider to make the UART interface work in the expected baud rate. |

| WDT                             | Enabled                                                                                                                                                                                                                                                      |

Figure 3-1 Operating Modes

# 3.1. Metering Mode

In the Default State, V9260F will enter the Metering Mode via some easy configurations:

- To select "CLK1" to source the clocks of the Vango metering architecture (MEACLK), UART serial interface (UARTCLK), and ADCs (ADCCLK)

- To enable or disable ADCs, to configure the sampling frequency to 819.2 kHz or 204.8 kHz, and to adjust the global biasing current to lower the power dissipation of ADCs

- To configure the MEACLK frequency to 3.2768 MHz or 819.2 kHz, which must be four or eight times of the ADCCLK frequency, and to configure the function of the Vango metering architecture

- To configure the baud rate of the UART serial interface through the "CKUDIV" bit (bit[4:2], SysCtrl, 0X0180)

In the Metering Mode, when a reset event, such as a POR, RX reset, or global software reset occurs, the chip will get back to the Default State.

Table 3-2 States of Functional Units in Metering Mode

| Functional Unit                 | State                                                                                                                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | Enabled by default                                                                                                                                                                       |

| Crystal oscillation circuit     | It is mandatory to set the bit "XRSTEN" to '1' to enable the function of stimulating the external crystal when it stops running.                                                         |

| 3.2-MHz RC oscillator           | It is recommended to disable this unit to lower the power dissipation. When the crystal oscillation circuit stops running, this unit will start to run automatically.                    |

| 32-kHz RC oscillator            | Enabled                                                                                                                                                                                  |

| Bandgap circuit                 | It is mandatory to enable this unit.                                                                                                                                                     |

| Biasing circuit                 | It is mandatory to enable this unit.                                                                                                                                                     |

| Power supply monitoring circuit | Enabled                                                                                                                                                                                  |

| POR circuit                     | Enabled                                                                                                                                                                                  |

| LDO                             | Enabled  Configure the DVCCLDO output voltage to lower the power dissipation of the Vango metering architecture                                                                          |

| ADC                             | Enable ADCs, configure the sampling frequency, and adjust the global biasing current to lower the power dissipation, to meet the application requirements                                |

| Vango metering architecture     | It is mandatory to enable this unit, and configure its functions to meet the application requirements.                                                                                   |

|                                 | Enabled                                                                                                                                                                                  |

| Interrupt management circuits   | Output the system control register self-checking interrupt and configuration verification interrupt all the time, and output the desired interrupts to meet the application requirements |

|                                 | Enabled                                                                                                                                                                                  |

| UART serial interface           | Baud rate is configured to meet the application requirements.                                                                                                                            |

|                                 | Enabled                                                                                                                                                                                  |