Specifications are subject to change without notice.

Copyright © 2022 Vango Technologies, Inc.

This document contains information that is proprietary to Vango Technologies, Inc. Unauthorized reproduction of this information in whole or in part is strictly prohibited.

# **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                                                      |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2015.06.05 | 0.1     | Initial release                                                                                                                                                                                                                                                                                  |

| 2015.10.08 | 0.2     | <ul> <li>Modified typical current load in sleeping mode from 10µA to 12µA</li> <li>Modified "0b000" to "0b001" in Table 18-10</li> <li>Updated Table 4-3 Allocation of Info Area</li> <li>Modified "SPC_FNC" to "SPCFNC" in Table 4-2</li> <li>Modified function description of "FWC"</li> </ul> |

| 2015 11 12 | 0.2     | Modified description of "CFWKEN" in Table 5-5                                                                                                                                                                                                                                                    |

| 2015.11.12 | 0.3     | <ul> <li>Updated Figure 4-2 Data Memory</li> <li>Set the bit of "BGPCHOPN" to '0' in Table 18-10 BandGap Control<br/>Register (CtrlBGP, 0x2862) to improve the temperature measurement<br/>performance.</li> </ul>                                                                               |

| 2016.01.06 | 0.4     | <ul> <li>Modified the registers and related content of temperature measurement and temperature calibration.</li> </ul>                                                                                                                                                                           |

|            |         | Updated Table 17-10 RTC Timing Registers                                                                                                                                                                                                                                                         |

|            |         | • Emphasized the setting of time information in sequence and at one time.                                                                                                                                                                                                                        |

|            |         | Modified "IOP14" to "P14WK", "PLLCNT" to "PLLCNTST"                                                                                                                                                                                                                                              |

| 2016.10.01 | 0.5     | Added V98XX Resource Comparison                                                                                                                                                                                                                                                                  |

|            |         | • Updated operating current in sleeping mode to $10\mu A$ and maximum current in sleeping mode to $14.5\mu A$ .                                                                                                                                                                                  |

| 2016.12.02 | 0.6     | Updated pin8 to NC                                                                                                                                                                                                                                                                               |

| 2010.12.02 | 0.0     | Updated 10.16.3 Measuring Battery Voltage and External Voltage                                                                                                                                                                                                                                   |

| 2018.05.31 | 3.0     | Modify the formula of Phase Compensation                                                                                                                                                                                                                                                         |

| 2010.03.31 | 5.0     | • Add V9811S/V9811A/V9811B/V9821/V9821S/V9881D                                                                                                                                                                                                                                                   |

|            |         | • Modify storage temperature to - $55 \sim 150$ C                                                                                                                                                                                                                                                |

| 2018.09.02 | 3.1     | Modify the input range of current and voltage channels                                                                                                                                                                                                                                           |

| 2010.07.02 | 5.1     | • Modify the maximum input voltage of analog comparator to LDO33                                                                                                                                                                                                                                 |

|            |         | Modify the LCD Drive Waveform                                                                                                                                                                                                                                                                    |

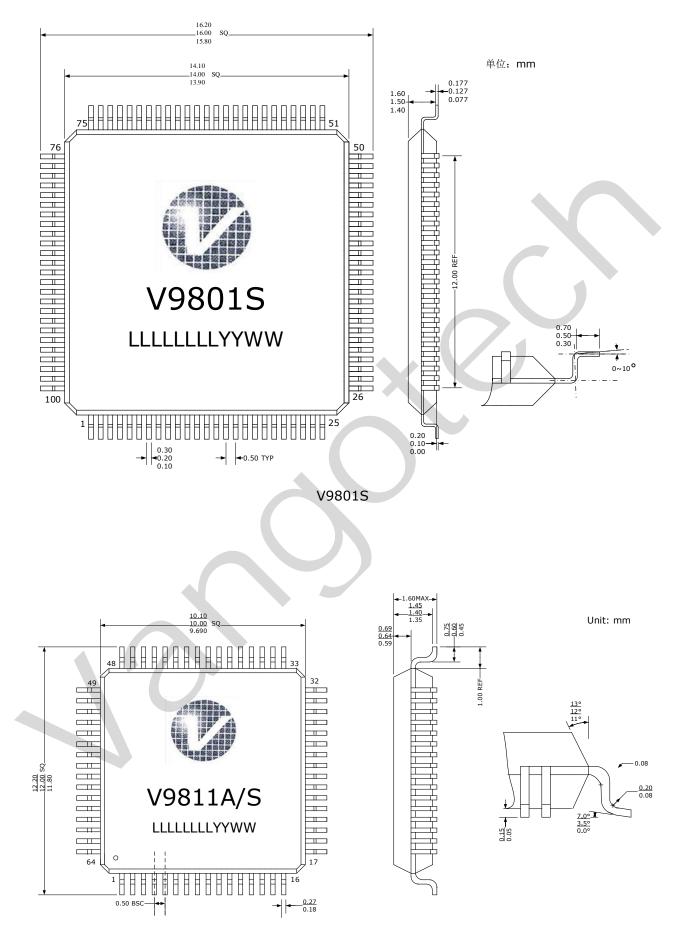

| 2021.03.01 | 3.2 | Modify V9811B Outline Dimensions |

|------------|-----|----------------------------------|

| 2021.04.15 | 3.3 | Update IEC Standard-             |

| 2021.06.02 | 3.4 | Update document format           |

| 2021.11.18 | 3.5 | Delete V9881D                    |

| 2022.01.22 | 3.6 | Add part marking                 |

# **General Description**

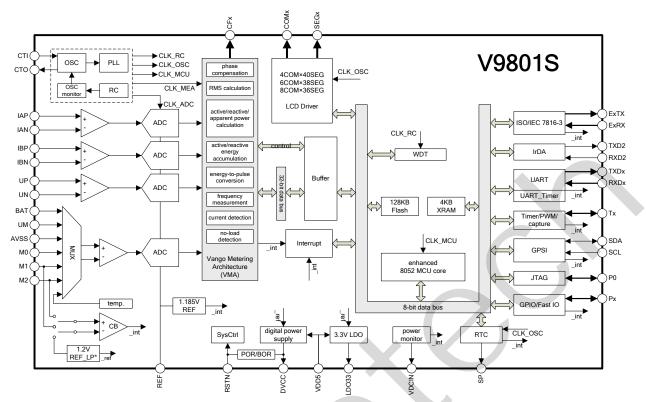

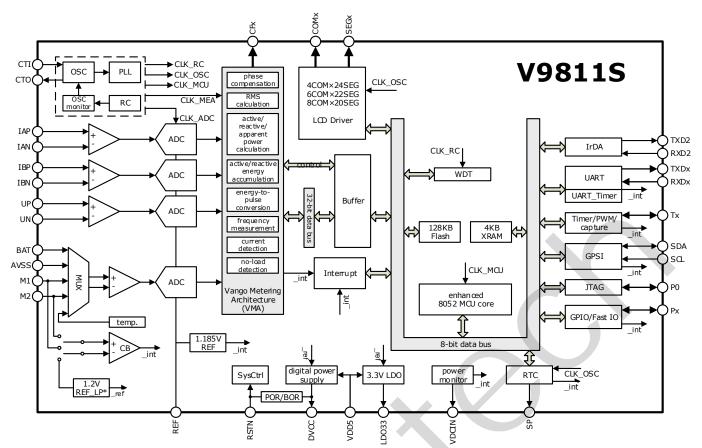

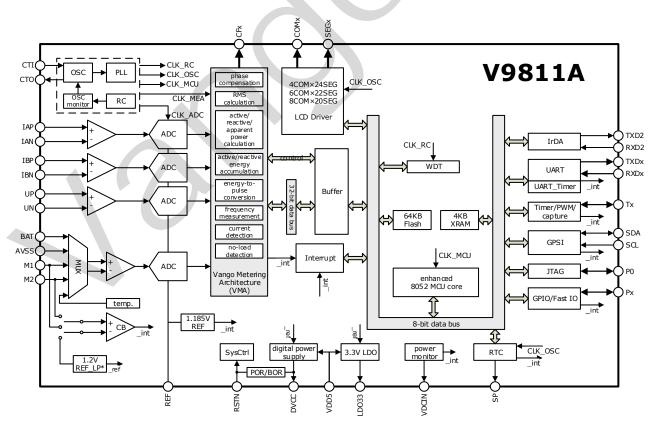

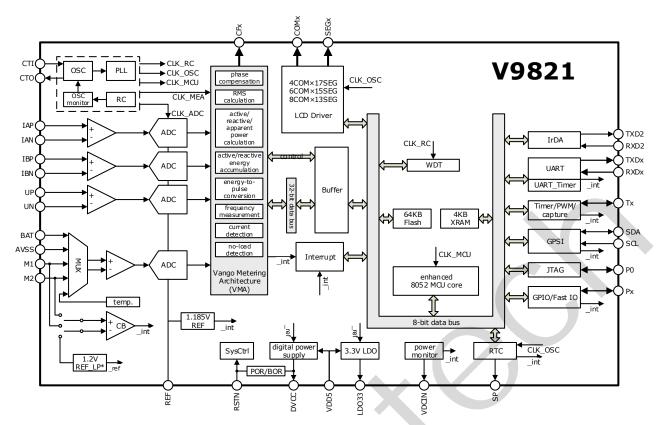

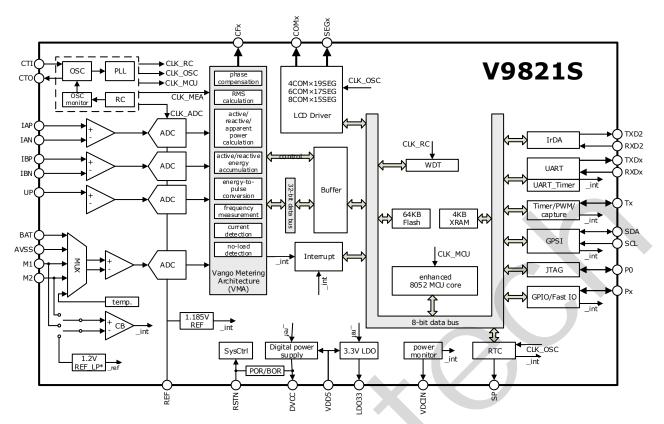

V98XX is a single-phase energy metering SoC chip, featuring very low power consumption and high performance. It integrates Analog Front-End (AFE), energy metering architecture, enhanced 8052 MCU core, RTC, WDT, Flash memory, RAM, and LCD driver. It can be used for the single-phase multi-functional energy meter applications.

### **Features**

- Optional power supply 3.3 V or 5 V, wide input range: 2.5 V to 5.5 V

- Reference voltage: 1.185 V (Typical drift 10 ppm/°C), interrupt triggered by external capacitor leakage

- Typical current load in full operation mode: 5.5 mA

- Typical current load in sleeping mode: 10 µA

- Supporting anti-tampering energy metering application

- Operating temperature: -40 °C ~ +85 °C

- Storage temperature: -55 °C ~ +150 °C

- Energy metering features:

- Four independent oversampling  $\Sigma/\Delta$  ADCs

- ✓ One voltage channel

- Two current channels, supporting shunt or CT for current sensing

- One multifunctional channel for various signal measurements

- High metering accuracy:

- Exceeding requirements of IEC 62053-21:2020/ IEC 62053-22:2020 and IEC 62053-23:2020

- ✓ Less than 0.1% error on active energy metering over dynamic range of 5000:1

- Less than 0.1% error on reactive

energy metering over dynamic range of 3000:1

- Less than 0.5% error on current/voltage RMS calculation over dynamic range of 1000:1

- Various measurements:

- Raw waveform and DC component of current and voltage signals

- Instantaneous/Average and active/reactive power

- Positive/Negative and active/reactive energy

- Average apparent power

- ✓ Instantaneous/Average current and voltage RMS

- ✓ Line frequency

- ✓ Temperature with measurement accuracy of ±1°C

- Battery voltage and external voltage signals

- Two current inputs for active energy metering, or one current input for active and reactive energy metering

- Programmable energy metering modes:

- Accumulating power, current RMS, or a constant for energy metering

- ✓ Accumulating energy at a

#### configurable frequency

- Calibrating meters via software:

- ✓ Phase compensation over a range of ±1.4° (min.), resolution of 0.0055°/lsb (min.).

- ✓ Gain calibration of RMS and power, and offset calibration of power

- ✓ Accelerating meter calibration when low current is applied

- CF pulse output and interrupt with configurable pulse width

- Zero-crossing interrupt

- Speeding current detection to lower power consumption

- Programmable threshold for no-load detection

- MCU and peripherals:

- High performance 8-bit 8052 MCU core, with programmable operation frequency, up to 26 MHz/6.5 mips

- One additional comparator

- Integrated oscillator, only one external 32768-Hz crystal is needed to generate crystal frequency

- Crystal supervised: Internal RC oscillator as a replacement when crystal oscillator stops running

- Integrated RTC and temperature sensor, digital crystal frequency compensation for calibration over temperature variation

- 128-KB Flash memory, ISP and IAP supported, with write protection and encryption function

- 4-KB extended SRAM memory

- Up to five UART serial interfaces, one supporting IR communication

- Up to two enhanced UART (EUART) serial interfaces, ISO/IEC 7816-3 compliant

- One GPSI (General-Purpose Serial Interface), I<sup>2</sup>C compliant

- Up to 54 programmable GPIOs, with port interrupt

- Up to 16 fast IOs

- Up to 12 hardware timers

- Supporting PWM output

- LCD driver:

- Up to 4×40, 6×38, or 8×36 segments

- / 1/3 bias or 1/4 bias ratio

- ✓ Configurable frame frequency

- ✓ Configurable drive voltage over a range of 2.7 V ~ 3.3 V, resolution 100 mV/lsb

- Various sleep/wakeup methods, configurable wakeup with reset

- Independent Watch-Dog Timer (WDT)

- Debugging via JTAG interfaces in real-time

| V98XX Resource Comparison |                                                                                                                                                         |                                                                                       |                                                                                    |                                                                                    |                                                                                                    |                                                                                    |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Peripherals               | V9801S                                                                                                                                                  | V9811S                                                                                | V9811A                                                                             | V9811B                                                                             | V9821                                                                                              | V9821S                                                                             |  |

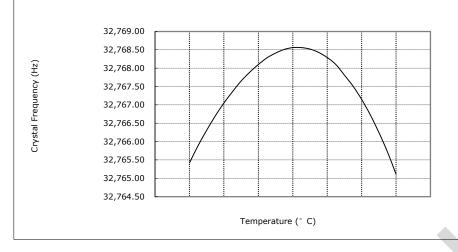

| Package                   | LQFP100                                                                                                                                                 | LQFP64                                                                                | LQFP64                                                                             | LQFP64(7*7)                                                                        | TQFP48                                                                                             | TQFP48                                                                             |  |

| Flash<br>memory           | 128KB                                                                                                                                                   | 128KB                                                                                 | 64KB                                                                               | 64KB                                                                               | 64KB                                                                                               | 64KB                                                                               |  |

| SRAM                      | 4KB                                                                                                                                                     | 4KB                                                                                   | 4КВ                                                                                | 4КВ                                                                                | 4КВ                                                                                                | 4KB                                                                                |  |

| UART                      | Up to 5<br>UART serial<br>interfaces,<br>one<br>supporting<br>IR<br>communica<br>tion; up to<br>2 EUART,<br>supporting<br>ISO/IEC<br>7816-3<br>protocol | Up to 4<br>UART serial<br>interfaces,<br>one<br>supporting<br>IR<br>communicat<br>ion | Up to 4 UART<br>serial<br>interfaces,<br>one<br>supporting IR<br>communicati<br>on | Up to 4 UART<br>serial<br>interfaces,<br>one<br>supporting IR<br>communicati<br>on | Up to 3 UART<br>serial<br>interfaces,<br>one<br>supporting IR<br>communicati<br>on                 | Up to 3 UART<br>serial<br>interfaces,<br>one<br>supporting IR<br>communicati<br>on |  |

| GPIO                      | 54                                                                                                                                                      | 43                                                                                    | 43                                                                                 | 43                                                                                 | 32                                                                                                 | 32                                                                                 |  |

| Rapid IO<br>port          | 16                                                                                                                                                      | 6                                                                                     | 6                                                                                  | 6                                                                                  | 2                                                                                                  | 1                                                                                  |  |

| LCD                       | Up to<br>$4 \times 40/6 \times 38$<br>$/8 \times 36$<br>segments,<br>1/3 bias or<br>1/4 bias<br>ratio                                                   | Up to<br>4×24/6×22<br>/8×20<br>segments,<br>1/3 bias or<br>1/4 bias<br>ratio          | Up to<br>4×24/6×22/<br>8×20<br>segments,<br>1/3 bias or<br>1/4 bias ratio          | Up to<br>4×24/6×22/<br>8×20<br>segments,<br>1/3 bias or<br>1/4 bias ratio          | Up to<br>$4 \times 17/6 \times 15/$<br>$8 \times 13$<br>segments,<br>1/3 Bias or<br>1/4 Bias ratio | Up to<br>4×19/6×17/<br>8×15<br>segments,<br>1/3 Bias or<br>1/4 Bias ratio          |  |

0

# **Table of Contents**

| Rev | vision               | Histor  | y2                                                  |  |  |  |  |

|-----|----------------------|---------|-----------------------------------------------------|--|--|--|--|

| Gei | General Description4 |         |                                                     |  |  |  |  |

| Fea | tures                |         | 4                                                   |  |  |  |  |

| Tat | ole of               | Conter  | nts7                                                |  |  |  |  |

| Fig | ure Li               | st      |                                                     |  |  |  |  |

| Tab |                      |         |                                                     |  |  |  |  |

| 1.  | Ele                  | ctrical | Characteristics                                     |  |  |  |  |

|     | 1.1.                 |         | te Maximum Ratings                                  |  |  |  |  |

|     | 1.2.                 | Energy  | Metering Specifications                             |  |  |  |  |

|     | 1.3.                 |         | Specifications                                      |  |  |  |  |

|     | 1.4.                 | -       | Interface Specifications                            |  |  |  |  |

|     | 1.5.                 | -       | y Specifications                                    |  |  |  |  |

|     | 1.6.                 |         | iming Specifications                                |  |  |  |  |

|     | 1.7.                 |         | Operating Current                                   |  |  |  |  |

|     |                      |         |                                                     |  |  |  |  |

| 2.  |                      |         | iptions28                                           |  |  |  |  |

| 3.  |                      |         | l Block Diagram43                                   |  |  |  |  |

| 4.  | 80                   |         | Core Architecture                                   |  |  |  |  |

|     | 4.1.                 | Memor   | ту Мар 47                                           |  |  |  |  |

|     | 4.2.                 | IRAM (  | Internal RAM) and SFRS (Special Function Registers) |  |  |  |  |

|     | 4.3.                 | Data M  | lemory                                              |  |  |  |  |

|     | 4.4.                 | Progra  | m Memory                                            |  |  |  |  |

|     | 4.5.                 | Instruc | tion Set                                            |  |  |  |  |

|     | 4                    | .5.1.   | Programmable MOVX Timing                            |  |  |  |  |

|     | 4                    |         | Dual Data Pointers                                  |  |  |  |  |

| 5.  | Re                   |         |                                                     |  |  |  |  |

| 0.  | 5.1.                 |         | 3                                                   |  |  |  |  |

|     | 5.2.                 |         | 2                                                   |  |  |  |  |

|     | 0.1                  |         | Power Recovery (Power up)67                         |  |  |  |  |

|     |                      |         |                                                     |  |  |  |  |

|     |                      |         | IO Wakeup Event                                     |  |  |  |  |

|     | _                    |         | RTC Wakeup Event                                    |  |  |  |  |

|     |                      |         | CF Pulse Wakeup Event                               |  |  |  |  |

|     |                      |         | 68                                                  |  |  |  |  |

|     | 5                    | .3.1.   | RSTn Pin Reset                                      |  |  |  |  |

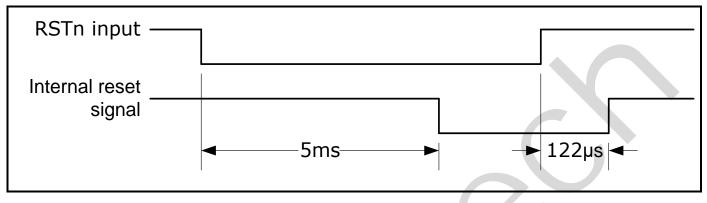

|     | 5                    | .3.2.   | Power-On Reset (POR) and Brown-Out Reset (BOR)69    |  |  |  |  |

|     | 5                    |         | WDT Overflow Reset                                  |  |  |  |  |

|     | 5.4.                 | Registe | ers                                                 |  |  |  |  |

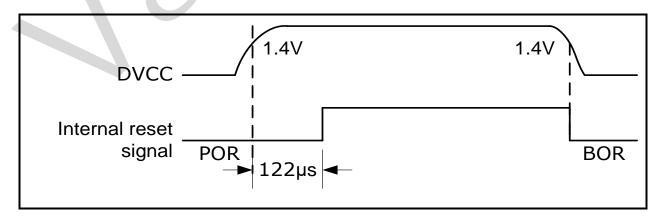

| 6.  | Clo                  |         | 74                                                  |  |  |  |  |

|     | 6.1.                 | RC Clo  | ck75                                                |  |  |  |  |

|     | 6.2.                 | OSC C   | lock                                                |  |  |  |  |

|     | 6.3.                 | PLL Clo | pck                                                 |  |  |  |  |

|    | 6.4. Sv | witchi | ng Source for CLK1 and CLK2                        | 77  |

|----|---------|--------|----------------------------------------------------|-----|

|    | 6.4.3   | 1. N   | lormal Operation                                   | 77  |

|    | 6.4.2   | 2. Ç   | Quick Operation                                    |     |

|    | 6.4.3   | 3. N   | lormal Operation vs. Quick Operation               |     |

|    | 6.5. Re | egiste | rs                                                 | 80  |

| 7. | Powe    | r Mar  | nagement                                           | 87  |

|    | 7.1. Pc | ower ( | Consumption                                        |     |

|    | 7.1.3   | 1. C   | DSC State                                          |     |

|    | 7.1.2   | 2. V   | Vorking State                                      |     |

|    | 7.1.3   | 3. S   | Sleeping State                                     |     |

|    |         | •      | rs                                                 |     |

| 8. | Powe    | r Sup  | oply                                               |     |

|    |         |        | egulator Circuit (LDO33)                           |     |

|    | 8.2. Di | igital | Power Supply                                       |     |

|    | 8.3. Pc | ower S | Supply Supervisor                                  |     |

|    |         |        | Supply                                             |     |

| 9. | Comp    | arato  | or                                                 | 101 |

| 10 |         |        | tering                                             |     |

| 10 |         |        | ssing to Registers for Vango Metering Architecture |     |

|    |         |        | ring Clock                                         |     |

|    |         |        | ence Voltage                                       |     |

|    |         |        | og Inputs                                          |     |

|    |         |        | og-to-Digital Conversion                           |     |

|    |         |        | ch of Current Channels                             |     |

|    |         |        | e Compensation                                     |     |

|    |         |        | al Input                                           |     |

|    |         | -      | ent Detection                                      |     |

|    | 10.10.  |        | S Calculation and Calibration                      |     |

|    | 10.11.  |        | parent Power Calculation                           |     |

|    | 10.12.  |        | ver Calculation and Calibration                    |     |

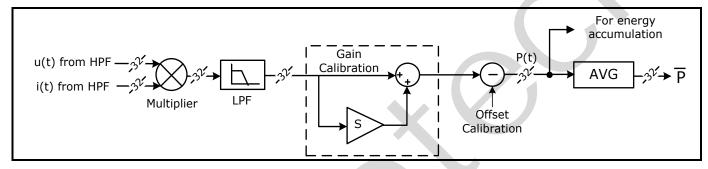

|    | 10.1    | 2.1.   | Active Power Calculation and Calibration           | 117 |

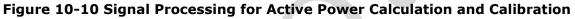

|    | 10.1    | 2.2.   | Reactive Power and Calibration                     | 117 |

|    | 10.13.  | Ene    | ergy Accumulation and CF Pulse Output              | 118 |

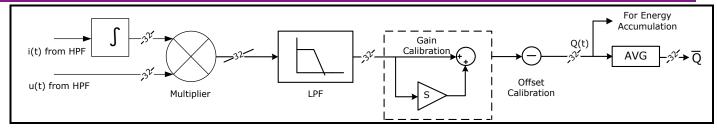

|    | 10.1    | 3.1.   | Energy Accumulation                                | 118 |

|    | 10.1    | 3.2.   | Energy Pulse Generation and CF Pulse Output        | 119 |

|    | 10.14.  | No-    | -Load Detection                                    |     |

|    | 10.15.  | Line   | e Frequency Measurement                            | 122 |

|    | 10.16.  | Mea    | asuring Various Signals in M Channel               | 123 |

|    | 10.1    | 6.1.   | Architecture of M Channel                          | 123 |

|    | 10.1    | 6.2.   | Measuring Temperature                              | 124 |

|    | 10.1    | 6.3.   | Measuring Battery Voltage and External Voltage     |     |

|    | 10.17.  | Init   | tializing Energy Metering Architecture             |     |

|    | 10.18.  | Cal    | ibration                                           | 127 |

|    | 10.1    |        | Registers for Meter Calibration                    |     |

|    | 10.1    | 8.2.   | Equations for Calibration                          | 128 |

|    | 10.1    | 8.3.   | Steps for Calibration                              | 130 |

| 11. | Inter | rrupt1                                  | 32  |

|-----|-------|-----------------------------------------|-----|

|     | 11.1. | Interrupt Sources 1                     | 132 |

|     | 11.2. | Interrupt Control Registers 1           | L37 |

|     | 11.3. | Interrupt Processing 1                  | L41 |

|     | 11.4. | Extended Interrupts 1                   | L42 |

|     | 11.4  | 4.1. Interrupt 8 1                      | L42 |

|     | 11.4  | 4.2. Interrupt 9 1                      | L44 |

|     | 11.4  | 4.3. Interrupt 10 1                     | L46 |

|     | 11.4  | 4.4. Interrupt 11 1                     | L48 |

| 12. | ΙΙΔΡΊ | T/Timers1                               | 50  |

| 12. | 12.1. | Timers/Counters                         |     |

|     |       | 1.1. TimerA                             |     |

|     |       | 1.2. Timer0/Timer1/Timer2               |     |

|     | 12.2. |                                         |     |

|     |       | 2.1. UART1                              |     |

|     | 12.2  |                                         |     |

|     | 12.3. |                                         |     |

|     |       | 3.1. Registers                          |     |

|     | 12.3  |                                         |     |

|     |       | 3.3. EUART Baud Rate Generation         |     |

|     |       | 3.4. Data Transmission and Reception    |     |

|     |       | 3.5. EUART for Smart Card Communication |     |

|     |       |                                         |     |

| 13. |       | eral-Purpose Serial Interface (GPSI)1   |     |

|     | 13.1. | Frame Structure 1                       |     |

|     | 13.2. | Serial Clock Generation                 |     |

|     | 13.3. | Receive and Transmit Data               |     |

|     | 13.4. | GPSI Interrupt 1                        |     |

|     | 13.5. | For I <sup>2</sup> C Application        | 190 |

|     | 13.6. | Registers 1                             | 192 |

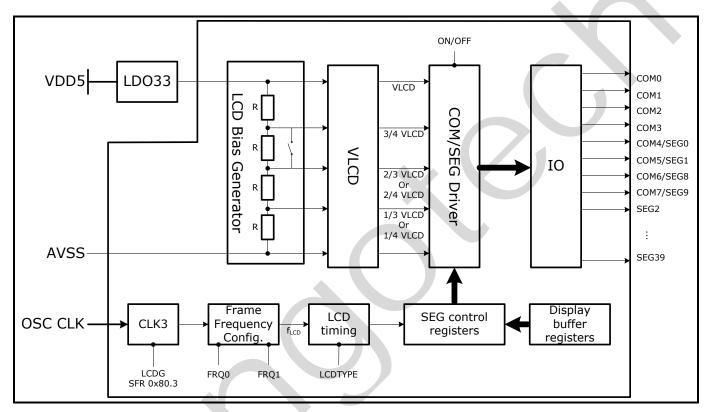

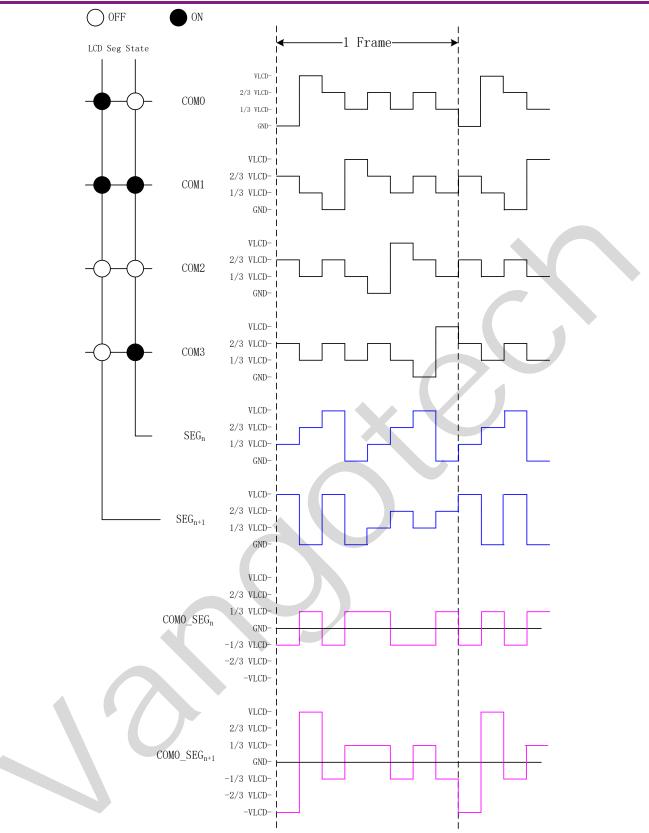

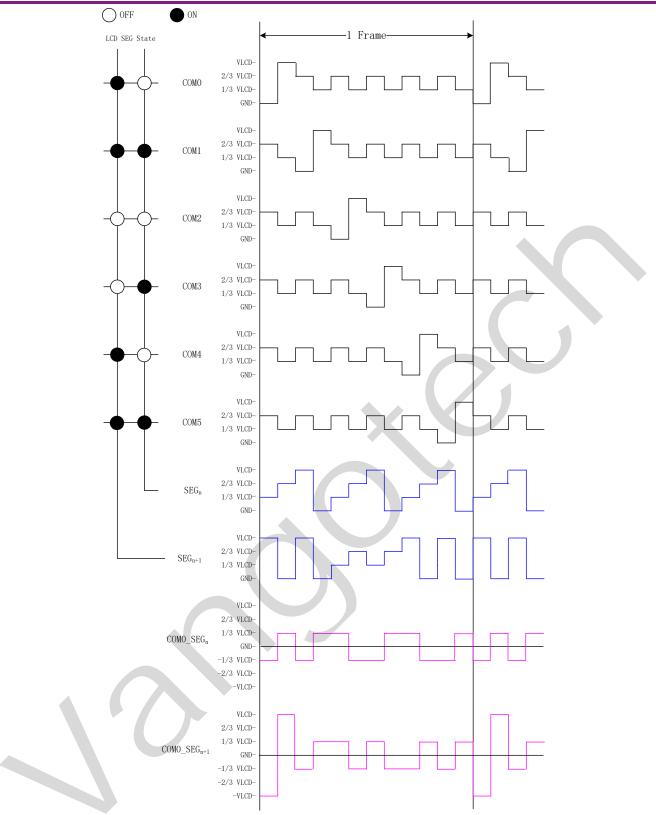

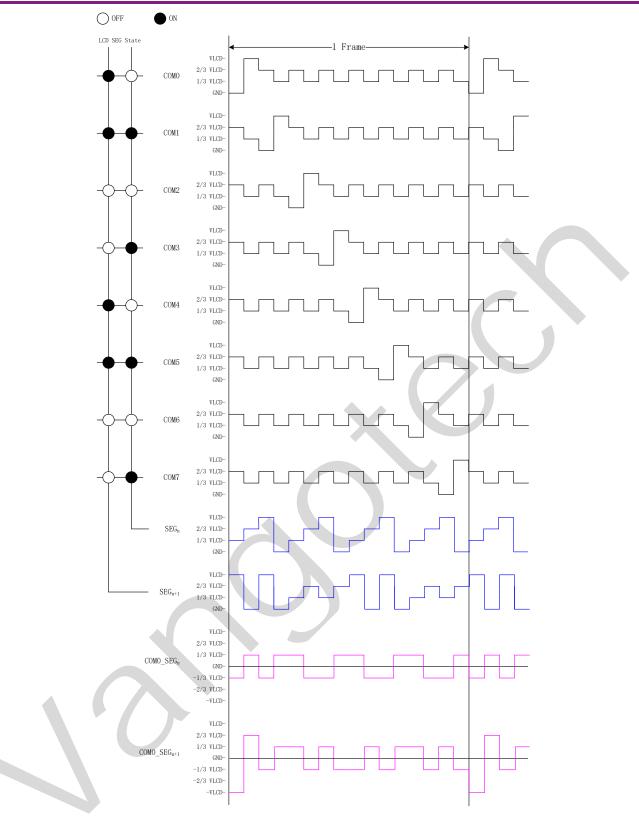

| 14. | LCD I | Driver1                                 | 95  |

|     | 14.1. | Pins for LCD Driver 1                   |     |

|     | 14.2. | LCD Timing 1                            | 196 |

|     | 14.3. | LCD Waveform Voltage 1                  | 196 |

|     | 14.4. | Display RAM 1                           | 196 |

|     | 14.5. | LCD Drive Waveform                      | 202 |

|     | 14.6. | Registers                               | 206 |

| 15. | CDTO  | 2                                       | 10  |

| 15. | 15.1. | P0                                      | -   |

|     | 15.2. | P1                                      |     |

|     | 15.3. | P2                                      |     |

|     | 15.4. | P3                                      | -   |

|     | 15.5. | P4                                      |     |

|     | 15.6. | P5                                      |     |

|     | 15.7. | P6                                      |     |

|     | 15.8. | P7                                      |     |

|     | 15.9. | P8                                      |     |

|     |       |                                         | -   |

|     | 15.10. | P9    |                                                    |     |

|-----|--------|-------|----------------------------------------------------|-----|

|     | 15.11. | P1    | 0                                                  |     |

| 16. | Watc   | hdog  | J Timer (WDT)                                      |     |

|     | 16.1.  | Cloc  | k for WDT                                          |     |

|     | 16.2.  | Clea  | ring WDT                                           |     |

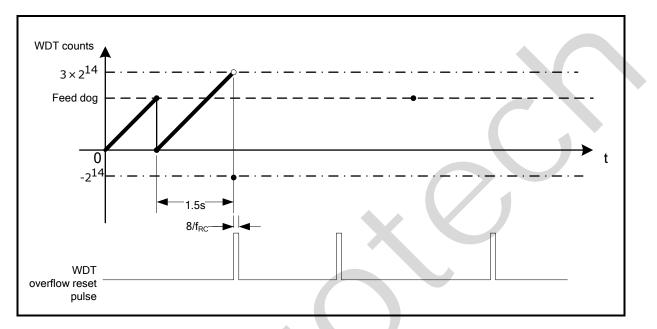

|     | 16.3.  | WDT   | Overflow Reset                                     | 233 |

| 17. | Real-  | Time  | e Clock (RTC)                                      |     |

|     | 17.1.  | Read  | ling and Writing of RTC Registers                  |     |

|     | 17.1   | l.1.  | Writing of RTC                                     |     |

|     | 17.1   | L.2.  | Reading of RTC                                     | 236 |

|     | 17.2.  | Timi  | ng                                                 |     |

|     | 17.3.  | RTC   | Interrupts                                         |     |

|     | 17.3   | 3.1.  | RTC Illegal Data Interrupt                         |     |

|     | 17.3   | 3.2.  | Pulse Output Interrupt per Second                  |     |

|     | 17.4.  | PLL   | Counter                                            |     |

|     | 17.5.  | Calit | prating RTC                                        |     |

|     | 17.5   | 5.1.  | Calibrating Pulse Frequency of PLL Counter         |     |

|     | 17.5   | 5.2.  | Calibrating Divided Pulse Frequency of PLL Counter |     |

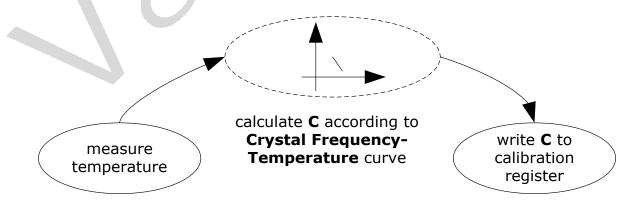

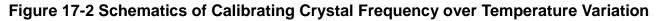

|     | 17.5   | 5.3.  | Crystal Frequency-Temperature Curve                |     |

|     | 17.6.  | Regi  | sters                                              |     |

| 18. | Regis  | sters |                                                    |     |

|     | 18.1.  | Anal  | og Control Registers                               |     |

|     | 18.2.  | Mete  | ering Control Registers                            |     |

|     | 18.3.  | Mete  | ering Data Registers                               | 256 |

|     | 18.4.  | Calib | pration Registers                                  |     |

| 19. | Outli  | ne D  | imensions                                          |     |

\*

# **Figure List**

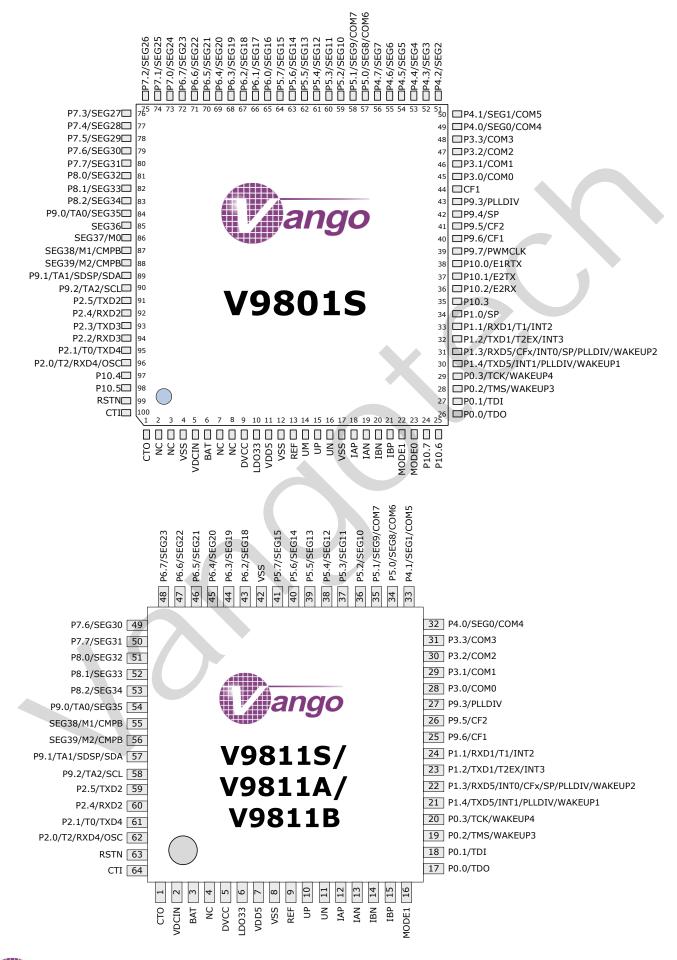

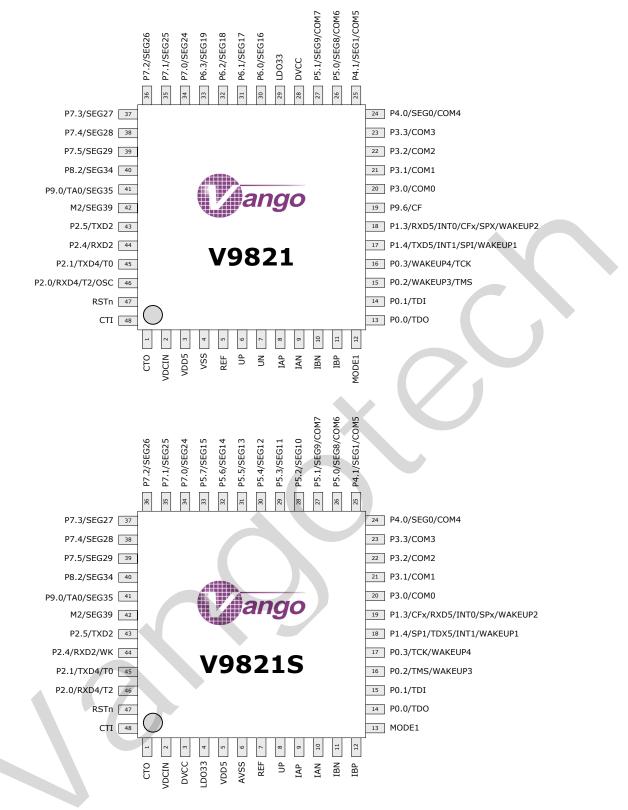

| Figure 2-1 Pin Assignment                                                                              |

|--------------------------------------------------------------------------------------------------------|

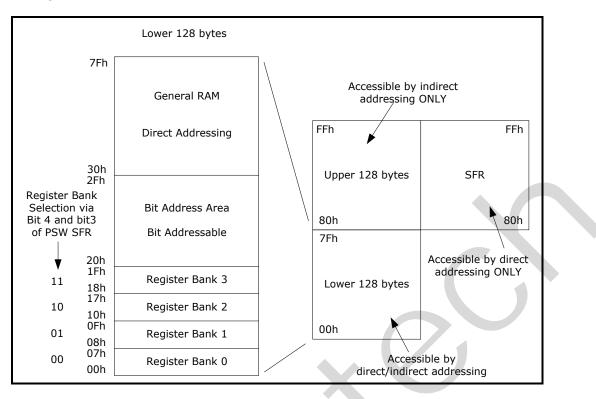

| Figure 4-1 IRAM and SFR 48                                                                             |

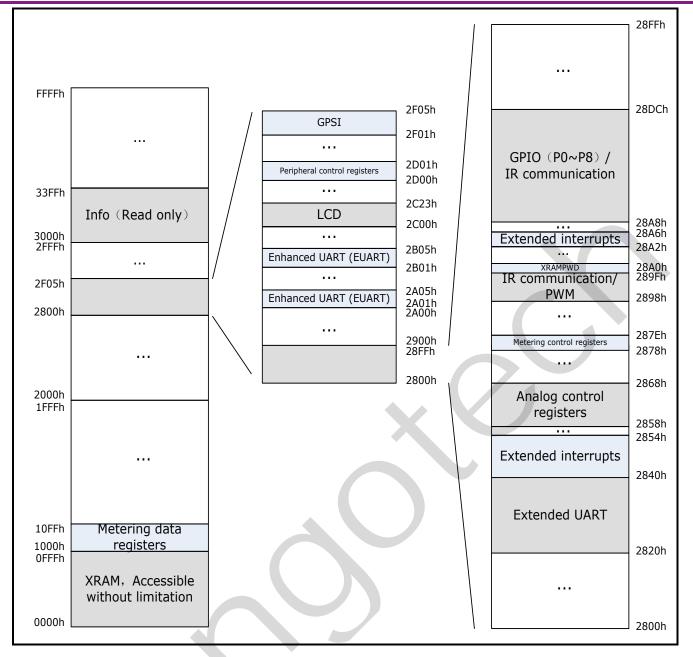

| Figure 4-2 Data Memory 52                                                                              |

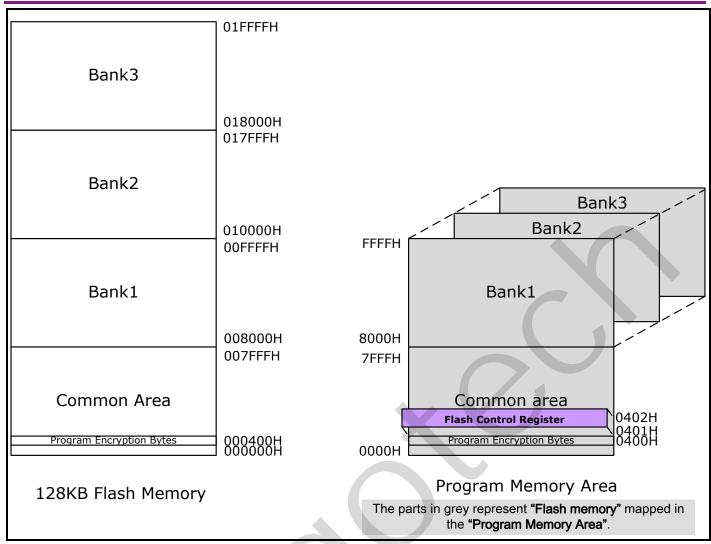

| Figure 4-3 Flash Memory and Program Memory Area57                                                      |

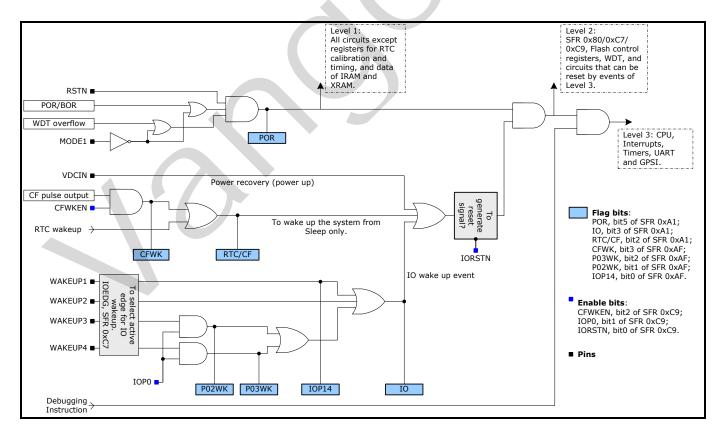

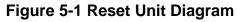

| Figure 5-1 Reset Unit Diagram                                                                          |

| Figure 5-2 RSTn Pin Reset Timing                                                                       |

| Figure 5-3 POR/BOR Timing                                                                              |

| Figure 6-1 Clock System Architecture                                                                   |

| Figure 6-2 Enabling PLL Circuit and Clock Source Switchover to PLL in Quick Operation 80               |

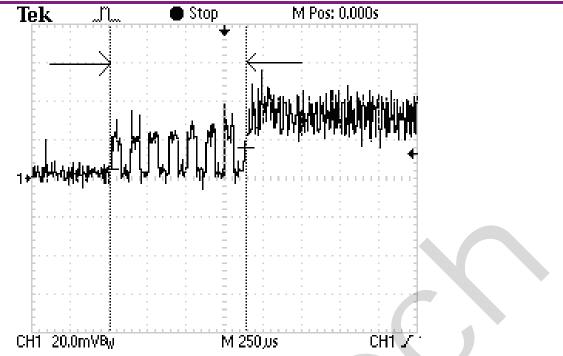

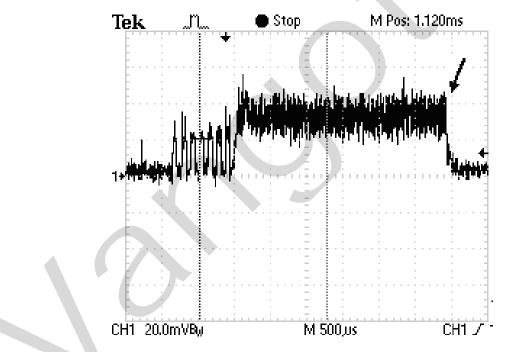

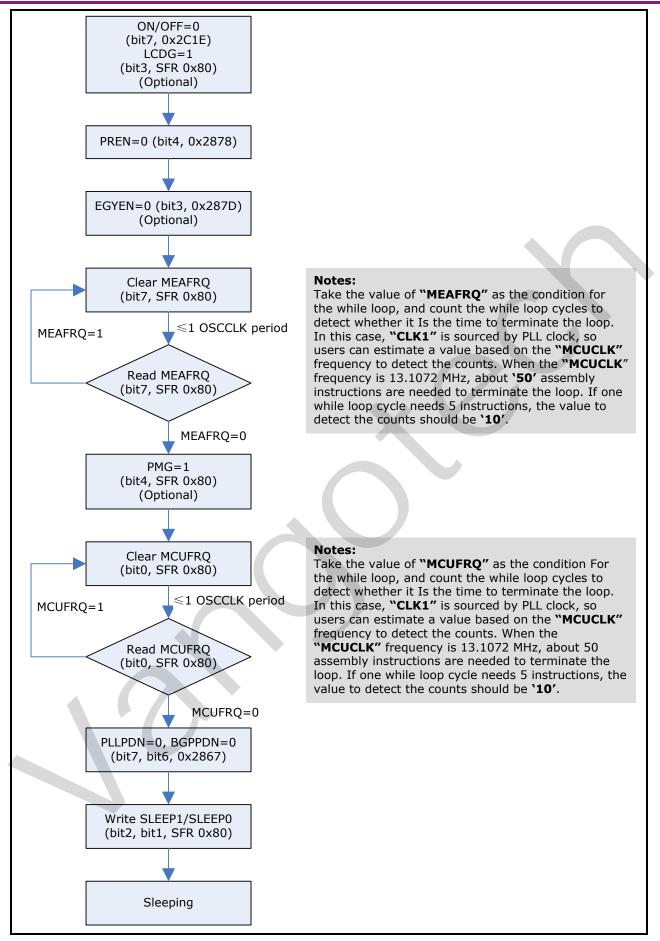

| Figure 6-3 Clock Source Switchover to OSC, Disabling PLL Circuit, Disabling CLK1 in Quick<br>Operation |

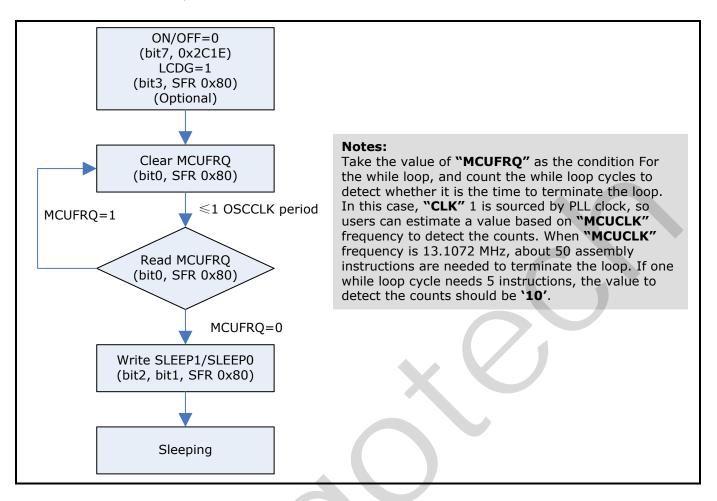

| Figure 7-1 Go to Sleeping State (Normal Method, Disable PLL Clock)                                     |

| Figure 7-2 Go to Sleeping State (Normal Method, PLL Clock Holds on)                                    |

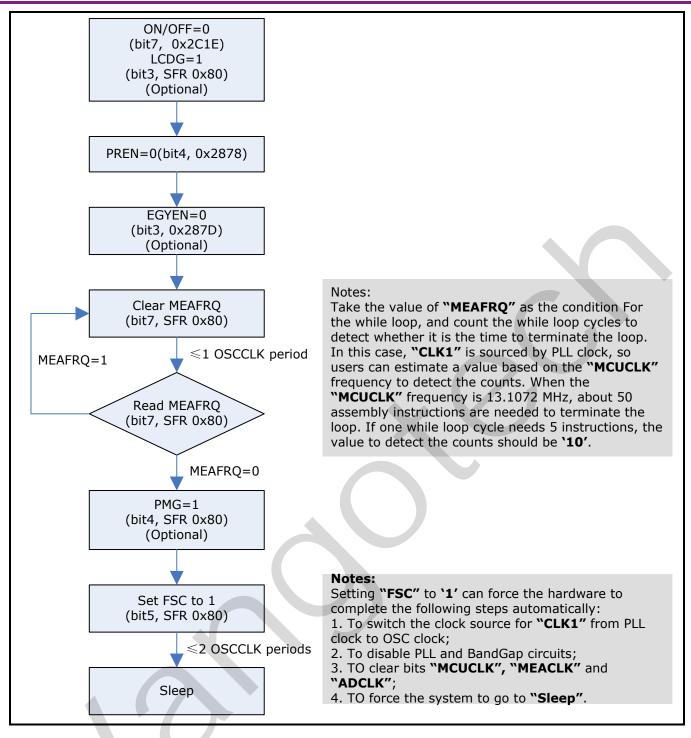

| Figure 7-3 Go to Sleep (Quick Method)                                                                  |

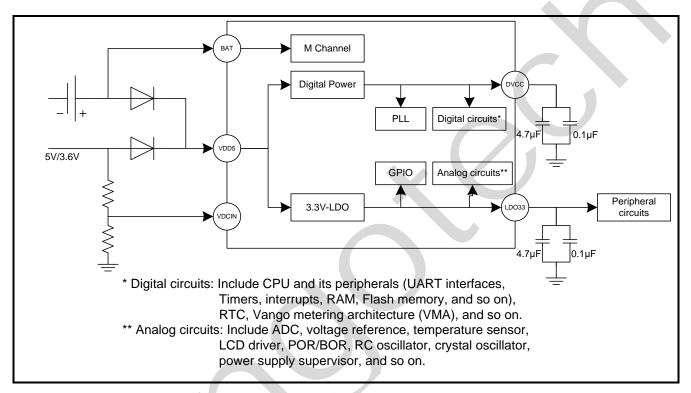

| Figure 8-1 Power Supply Architecture                                                                   |

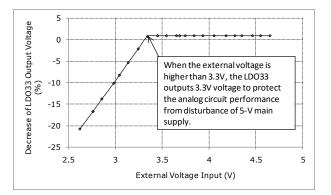

| Figure 8-2 LDO33 Output and 5V Power Input                                                             |

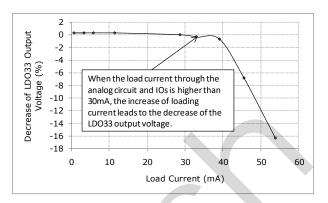

| Figure 8-3 LDO33 output and the Load Current                                                           |

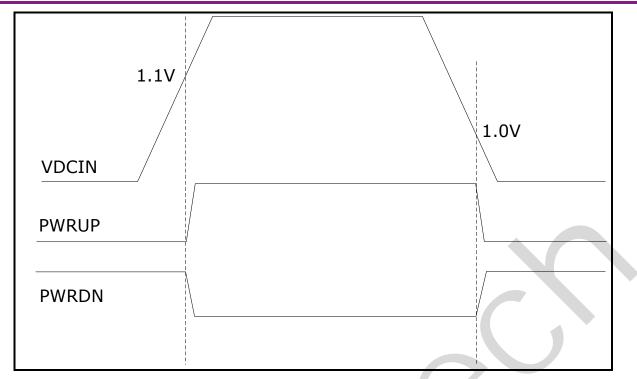

| Figure 8-4 Relationship between VDCIN Input Signal and States of Flag Bits PWRUP and<br>PWRDN          |

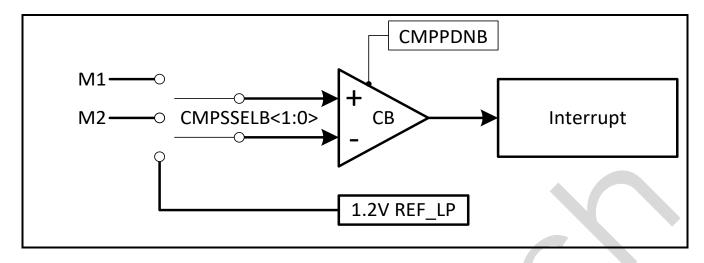

| Figure 9-1 Comparator Architecture 101                                                                 |

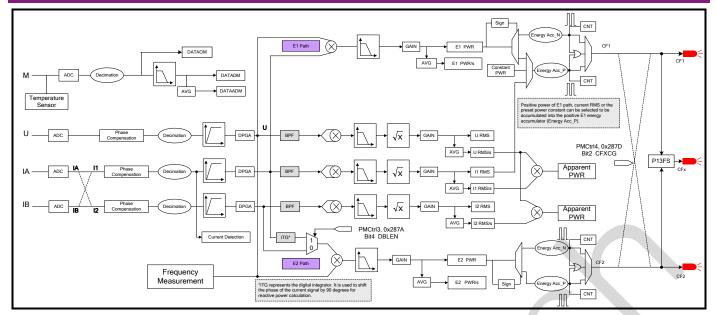

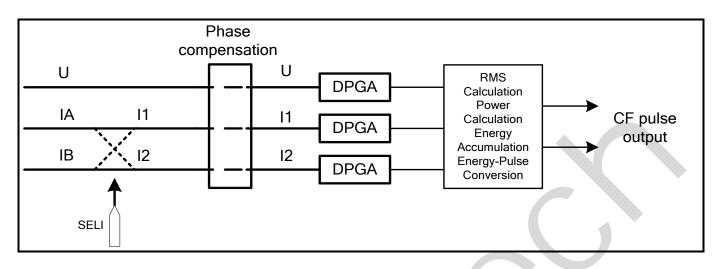

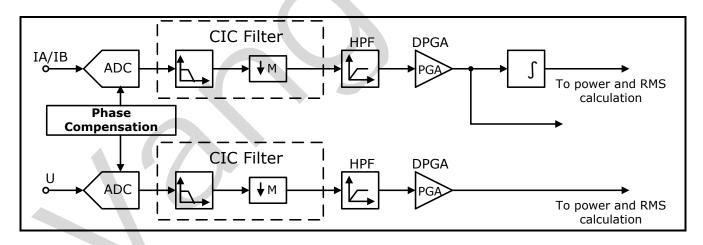

| Figure 10-1 Digital Signal Processing in Vango Metering Architecture 104                               |

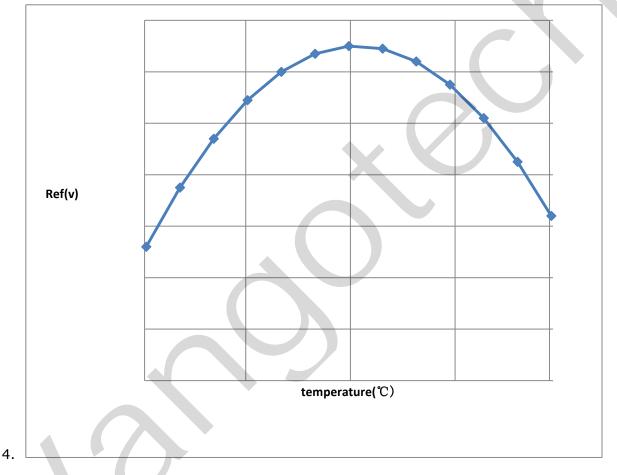

| Figure 10-2 The temperature characteristic curve of reference voltage                                  |

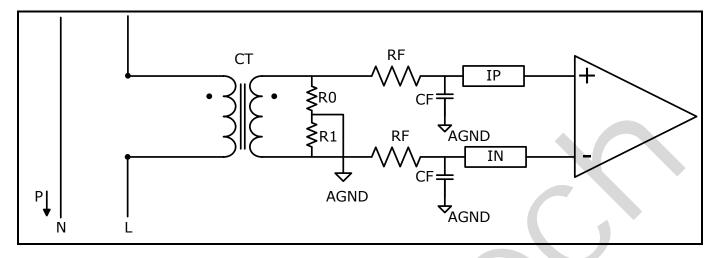

| Figure 10-3 CT for Current Analog Input                                                                |

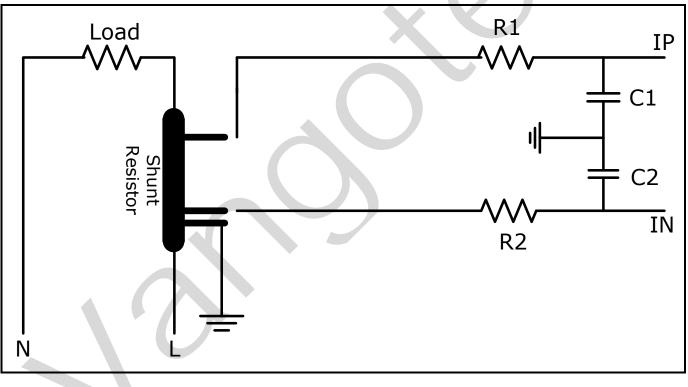

| Figure 10-4 Shunt Resistor Network for Current Analog Input                                            |

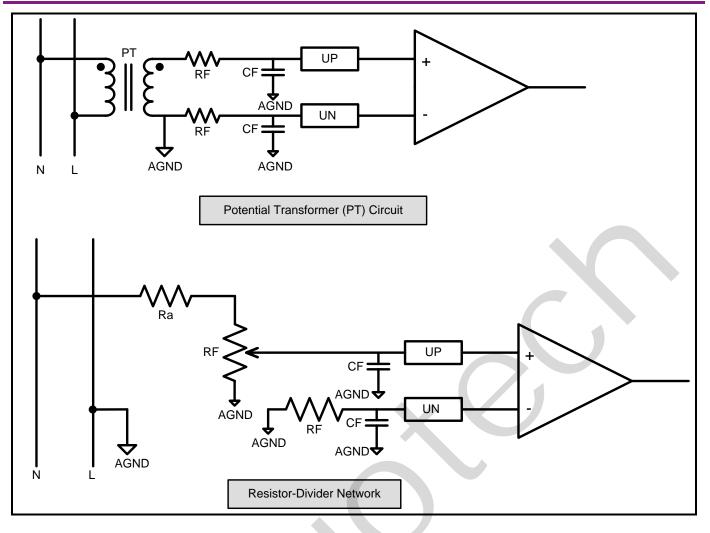

| Figure 10-5 Analog Input of Voltage                                                                    |

| Figure 10-6 Exchange of Current Channels 110                                                           |

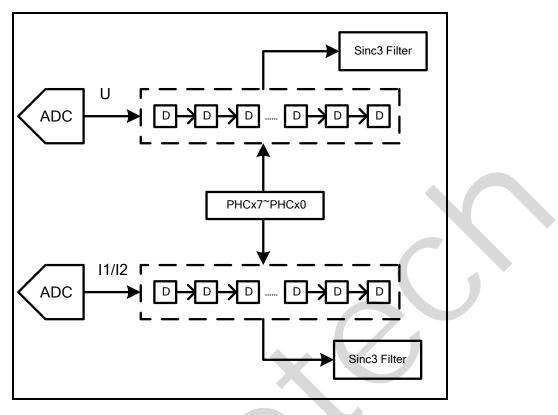

| Figure 10-7 Phase Compensation Schematics 111                                                          |

| Figure 10-8 Digital Inputs                                                                             |

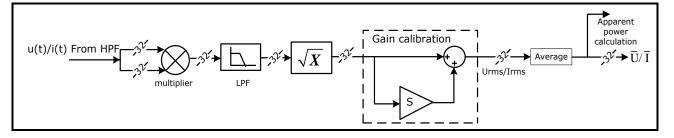

| Figure 10-9 RMS Calculation and Calibration 116                                                        |

| Figure 10-12 Energy Accumulation and CF Pulse Output                                                   |

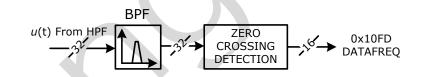

| Figure 10-13 Signal Processing for Line Frequency Measurement 122                                      |

| Hangzhou Vango Technologies, Inc.11 / 264                                                              |

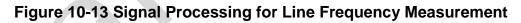

| Figure 10-14 M Channel Architecture                                                  | . 123 |

|--------------------------------------------------------------------------------------|-------|

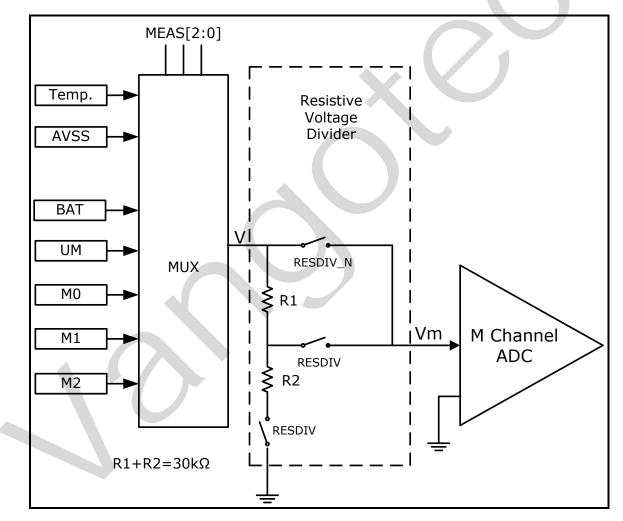

| Figure 10-15 Signal Processing in M Channel                                          | . 124 |

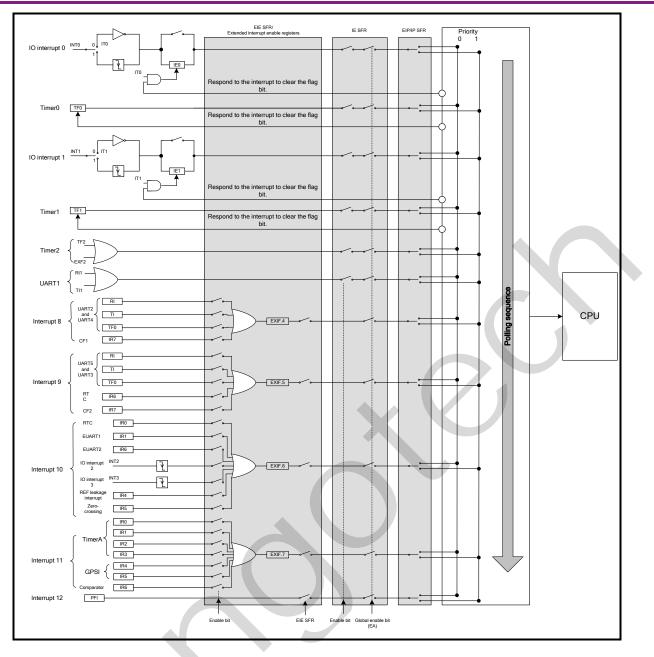

| Figure 11-1 Interrupt Logic                                                          | . 137 |

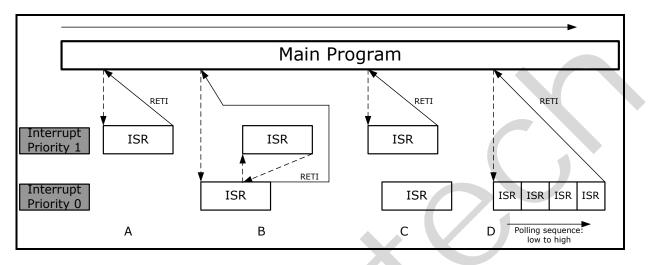

| Figure 11-2 Interrupt Processing                                                     | . 141 |

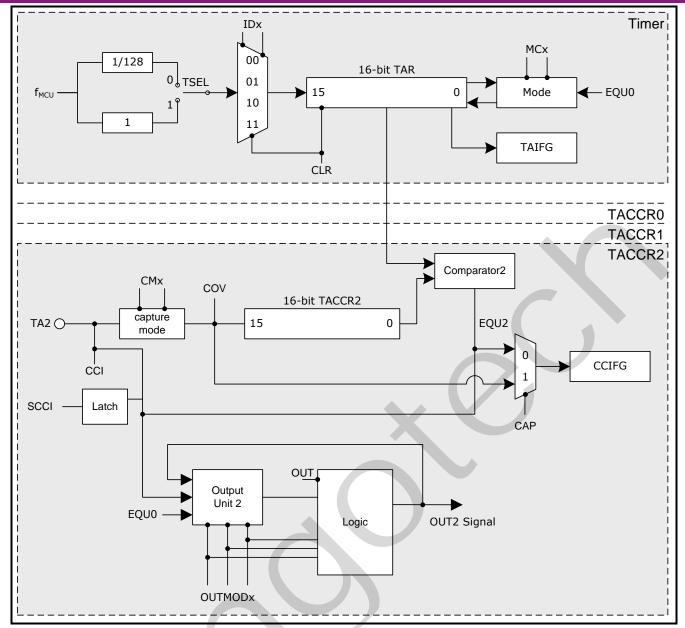

| Figure 12-1 TimerA Architecture                                                      | . 151 |

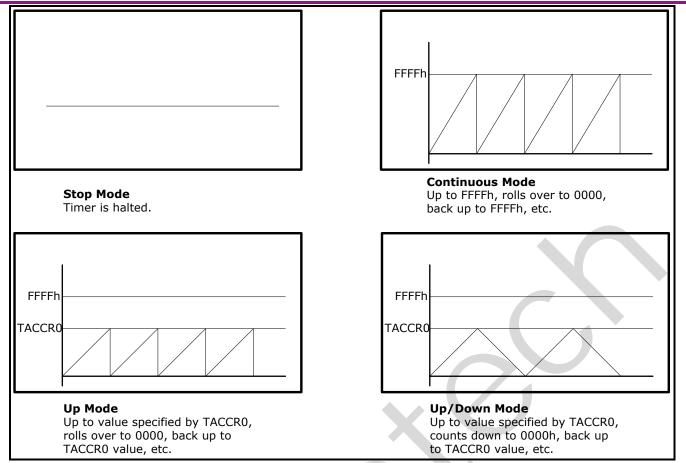

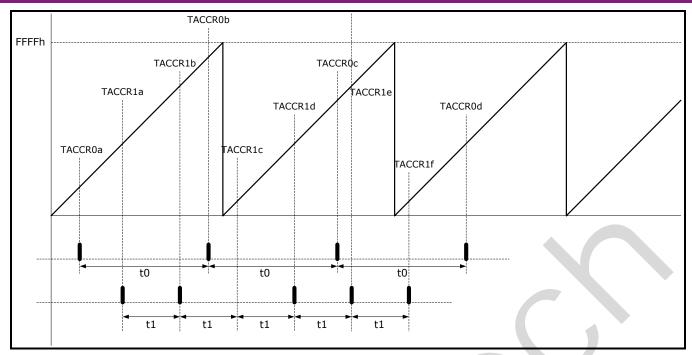

| Figure 12-2 Operation Modes for TimerA                                               | . 154 |

| Figure 12-3 Configuring Output Frequency in Continuous Mode                          | . 155 |

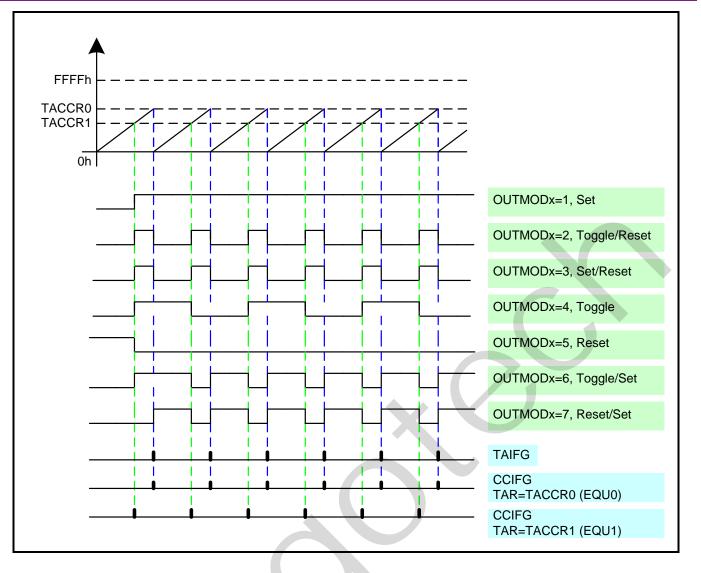

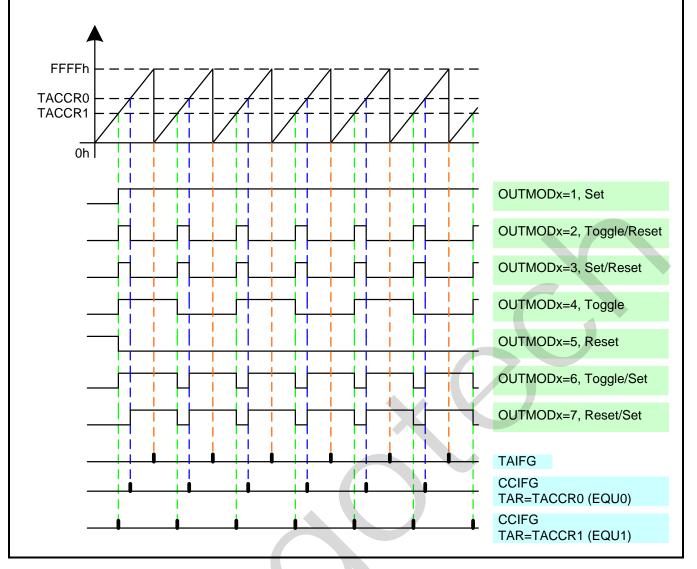

| Figure 12-4 Output on Pin TA1 in Up Mode                                             | . 159 |

| Figure 12-5 Output on Pin TA1 in Continuous Mode                                     | . 160 |

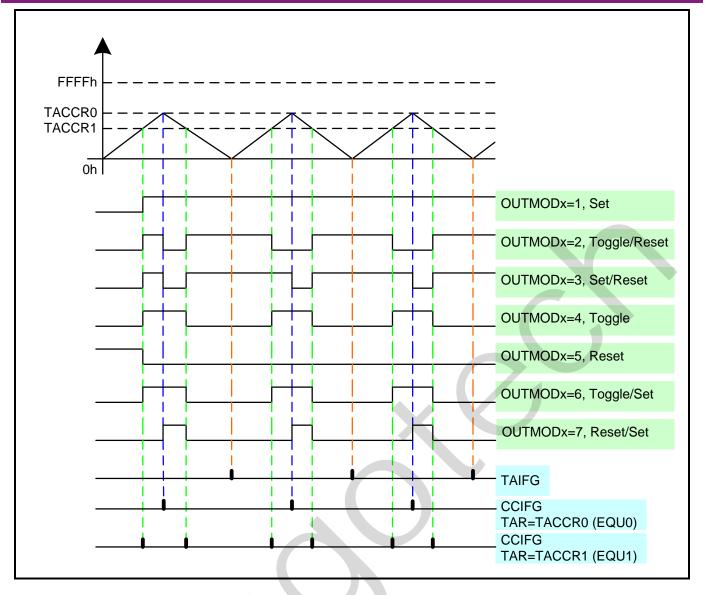

| Figure 12-6 Output on Pin TA1 in Up/Down Mode                                        | . 161 |

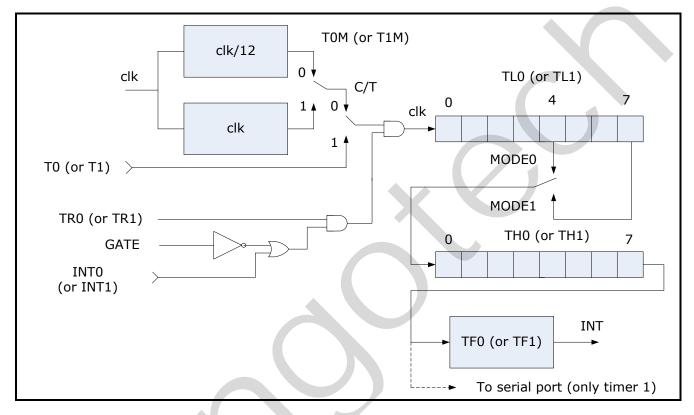

| Figure 12-7 Timer 0/1, Mode 0/1                                                      | . 165 |

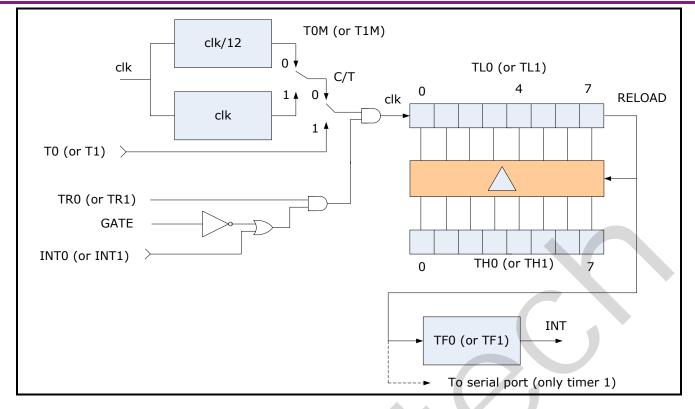

| Figure 12-8 Timer 0/1, Mode 2                                                        | . 166 |

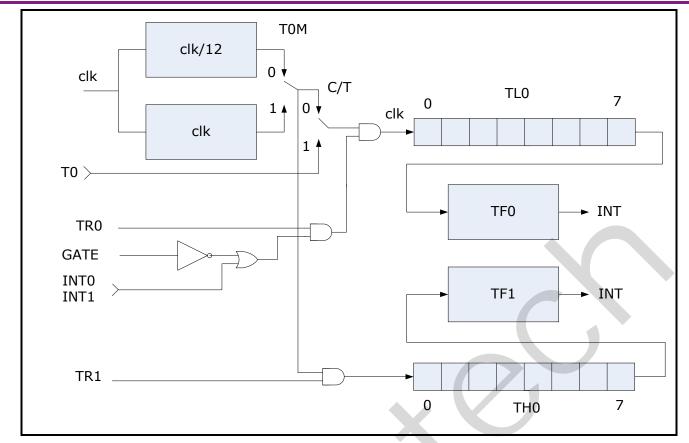

| Figure 12-9 Timer 0, Mode 3                                                          | . 167 |

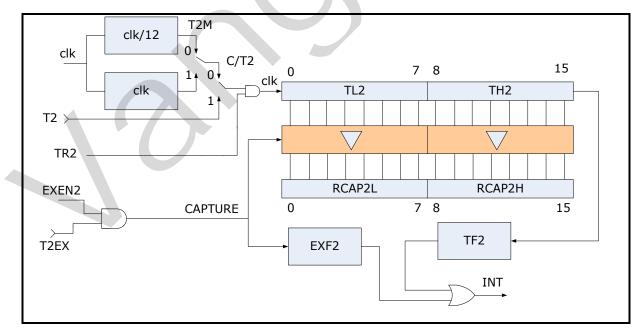

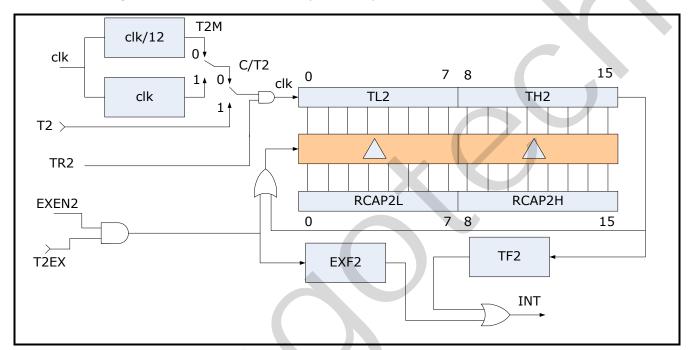

| Figure 12-10 Timer2, 16-bit Timer/ Counter in Capture Mode                           | . 169 |

| Figure 12-11 Timer2, 16-Bit Timer/Counter in Auto-Reload Mode                        |       |

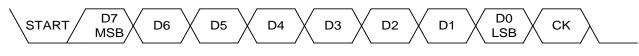

| Figure 12-12 Data Frame in EUART Communication                                       | . 181 |

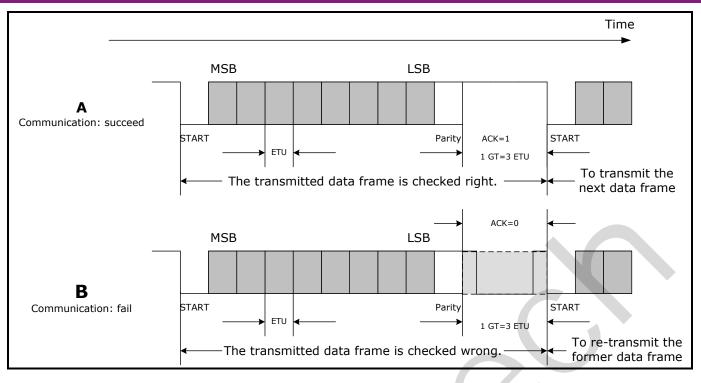

| Figure 12-13 EUART Communication Timing                                              | . 184 |

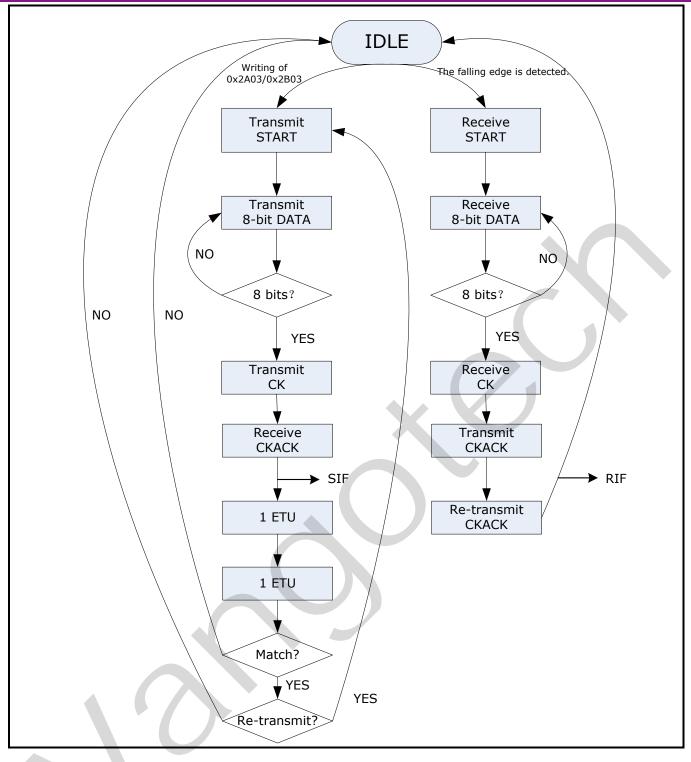

| Figure 12-14 Data Transmission and Reception                                         | . 186 |

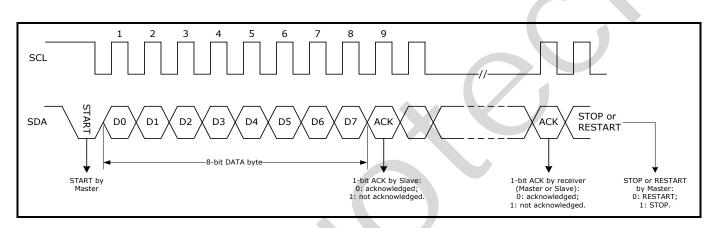

| Figure 13-1 Frame Structure on SDA                                                   | . 188 |

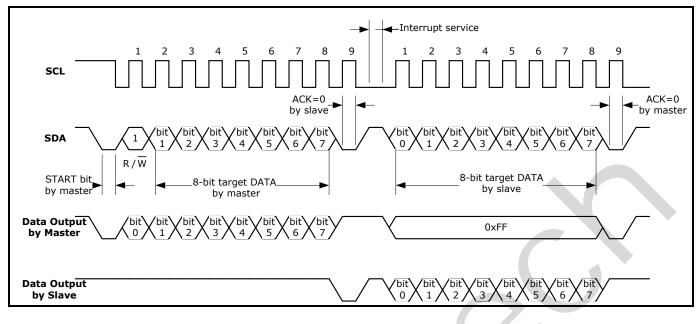

| Figure 13-2 Receive and Transmit Data                                                | . 190 |

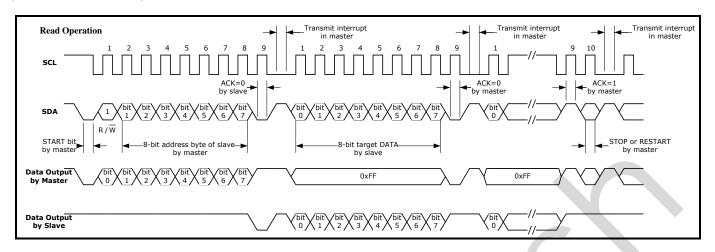

| Figure 13-3 Read Operation                                                           | . 191 |

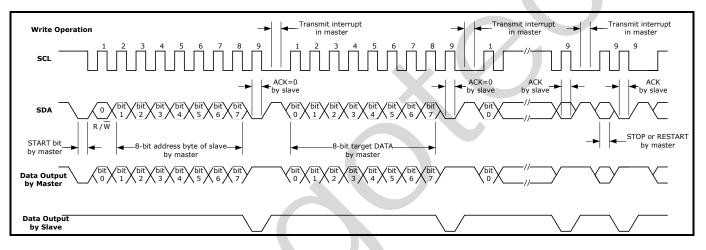

| Figure 13-4 Write Operation                                                          | . 191 |

| Figure 14-1 LCD Driver Block Diagram                                                 | . 195 |

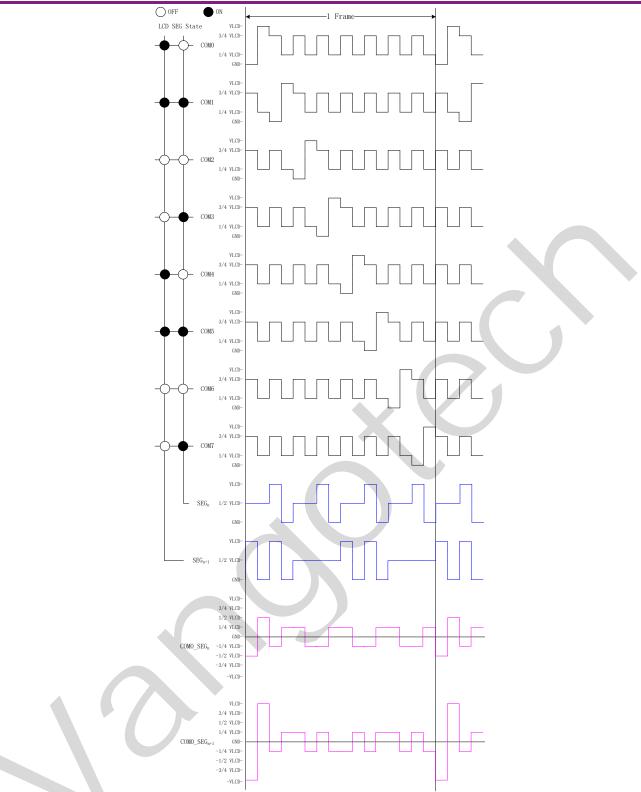

| Figure 14-2 LCD Drive Waveform When an LCD Panel of 1/4 Duty and 1/3 Bias is Applied | . 203 |

| Figure 14-3 LCD Drive Waveform When an LCD Panel of 1/6 Duty and 1/3 Bias is Applied | . 204 |

| Figure 14-4 LCD Drive Waveform When an LCD Panel of 1/8 Duty and 1/3 Bias is Applied | . 205 |

| Figure 14-5 LCD Drive Waveform When an LCD Panel of 1/8 Duty and 1/4 Bias is Applied | . 206 |

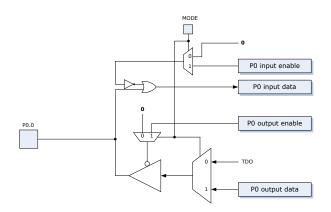

| Figure 15-1 Architecture of P0.0                                                     | . 211 |

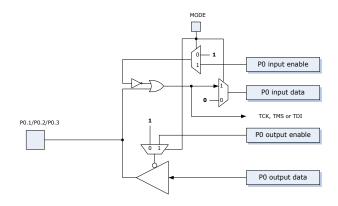

| Figure 15-2 Architecture of P0.1/P0.2/P0.3                                           | . 211 |

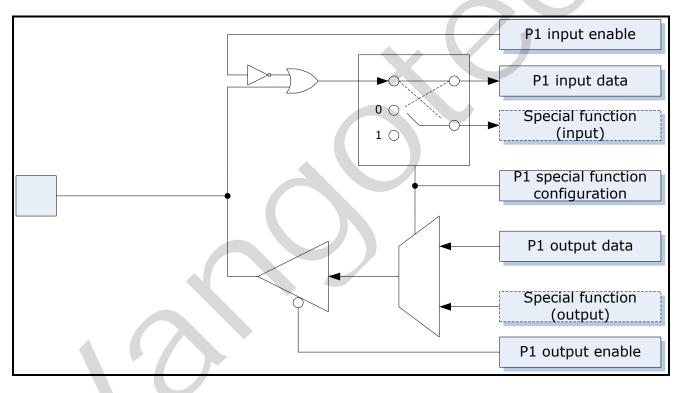

| Figure 15-3 Architecture of Each Port of Group P1                                    | . 212 |

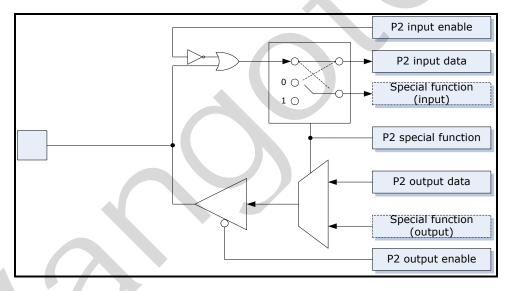

| Figure 15-4 Architecture of Each Port of Group P2                                    | . 215 |

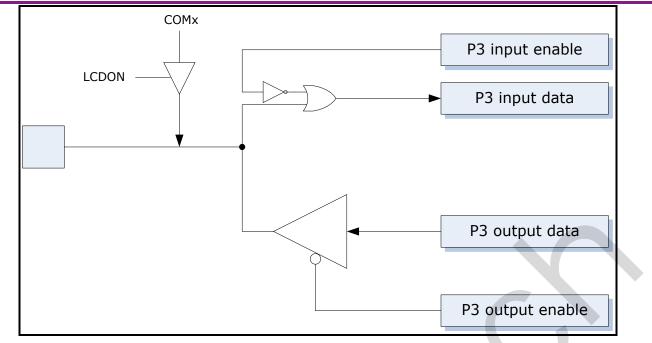

| Figure 15-5 Architecture of Each Port of Group P3                                    | . 218 |

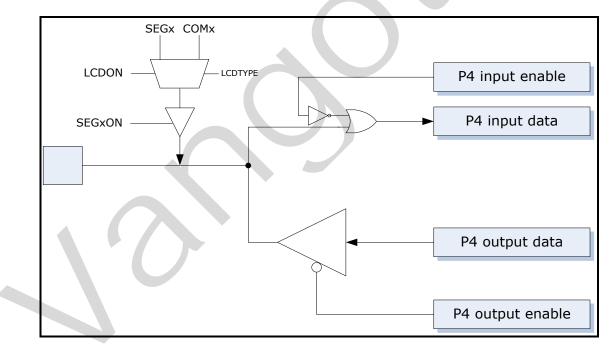

| Figure 15-6 Architecture of Each Port of Group P4                                  | . 219 |

|------------------------------------------------------------------------------------|-------|

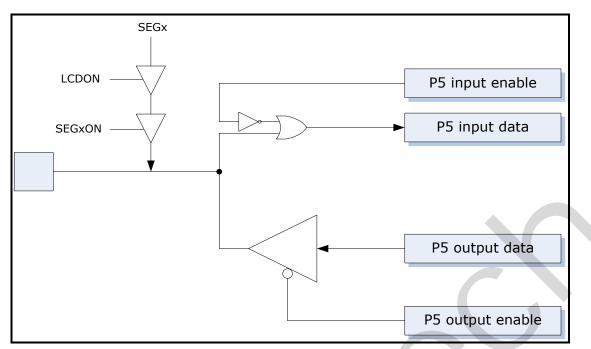

| Figure 15-7 Architecture of Each Port of Group P5                                  | . 221 |

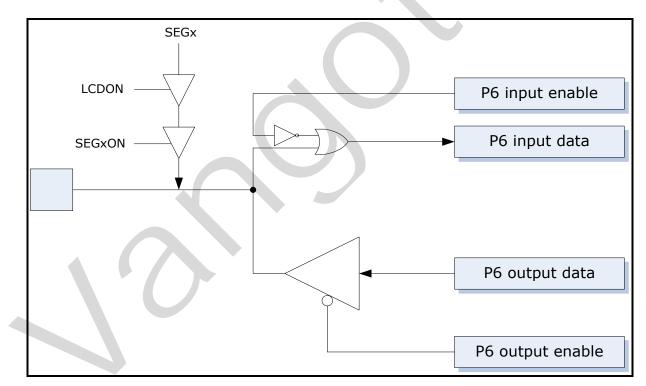

| Figure 15-8 Architecture of Each Port of Group P6                                  | . 222 |

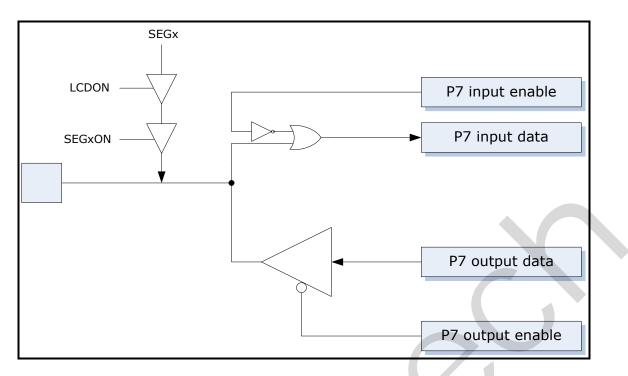

| Figure 15-9 Architecture of Each Port of Group P7                                  | . 224 |

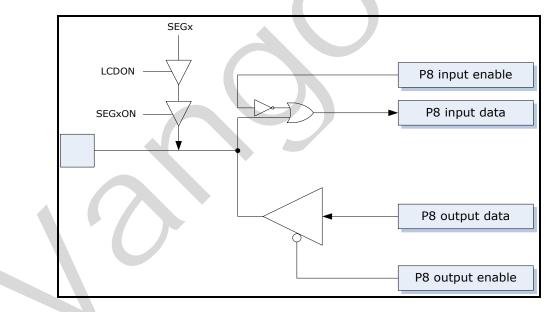

| Figure 15-10 Architecture of Each Port of Group P8                                 | . 225 |

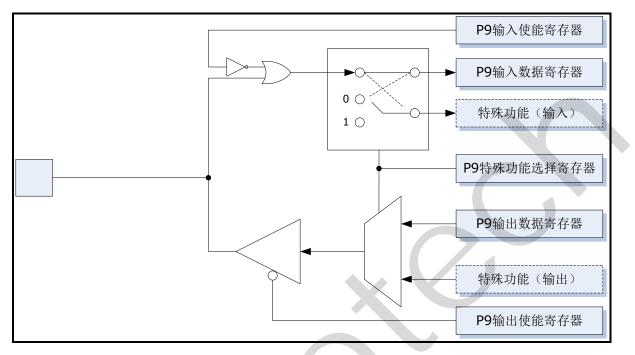

| Figure 15-11 Architecture of Each Port of Group P9                                 | . 227 |

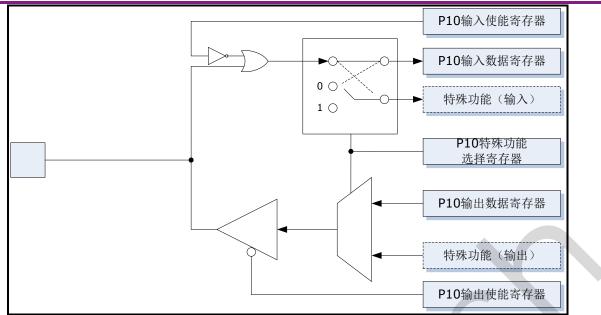

| Figure 15-12 Architecture of Each Port of Group P10                                | . 230 |

| Figure 16-1 WDT Overflow Reset                                                     | . 234 |

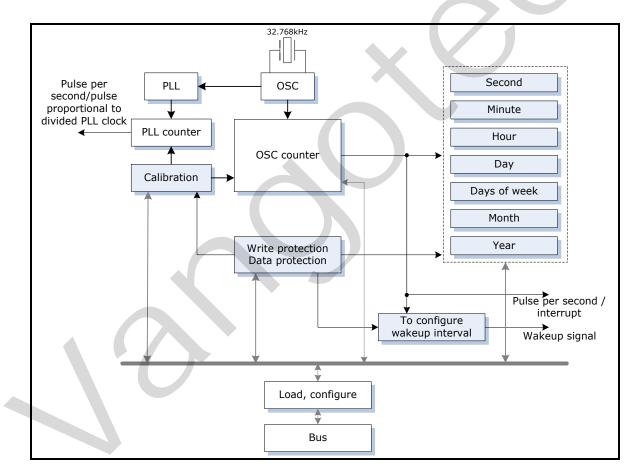

| Figure 17-1 Architecture of RTC                                                    | . 235 |

| Figure 17-2 Schematics of Calibrating Crystal Frequency over Temperature Variation | . 239 |

| Figure 17-3 Crystal Frequency-Temperature Curve                                    | . 240 |

# **Table List**

| Table 1-1 Absolut Maximum Ratings                                                    | 22   |

|--------------------------------------------------------------------------------------|------|

| Table 1-2 Energy Metering Specifications                                             | 22   |

| Table 1-3 Analog Specifications                                                      | 23   |

| Table 1-4 Digital Interface Specifications                                           | 25   |

| Table 1-5 Memory Specifications                                                      | 25   |

| Table 1-6 GPSI Timing Specifications                                                 | 26   |

| Table 1-7 Typical Operating Current                                                  | 26   |

| Table 2-1 Pin Descriptions (Pin type: "O"=Output, "I"= Input, "P"=Power, "G"=Ground) | 30   |

| Table 4-1 Select a Register Bank                                                     |      |

| Table 4-2 Special Function Registers (SFR)                                           |      |

| Table 4-3 Allocation of Info Area                                                    | 52   |

| Table 4-4 Flash Control Register 1 (FCtrl1, 0x0402)                                  | 56   |

| Table 4-5 Code Bank Register (CBANK, SFR 0xA0)                                       | 57   |

| Table 4-6 Programming Flash Memory                                                   | 58   |

| Table 4-7 Instruction Set                                                            | 59   |

| Table 4-8 Programmable MOVX Timing                                                   | 64   |

| Table 5-1 Circuits to Be Reset                                                       | 65   |

| Table 5-2 System State Register, Systate (SFR 0xA1)                                  | 70   |

| Table 5-3 P0 IO Wakeup Flag Register (IOWKDET, SFR 0xAF)                             | 70   |

| Table 5-4 IO Wakeup Edge Control Register (IOEDG, SFR 0xC7)                          | 71   |

| Table 5-5 IO Wakeup Control Register (IOWK, SFR 0xC9)                                | . 72 |

| Table 5-6 Set RTC Wake-Up Interval                                                   | 72   |

| Table 5-7 RTC Seconds Wake-up Interval Configuration Register (SECINT, SFR 0xDF)     | 72   |

| Table 6-1 Comparing Normal, Quick, and Combination Operation                         | 79   |

| Table 6-2 Clock Switchover Control Register (SysCtrl, SFR 0x80)                      | 80   |

| Table 6-3 Peripheral Control Register 0 (PRCtrl0, 0x2D00)                            | 82   |

| Table 6-4 Peripheral Control Register 1 (PRCtrl1, 0x2D01)                            | 83   |

| Table 6-5 Register 1 to Adjust OSC Clock Frequency                                   | 83   |

| Table 6-6 Register 2 to Adjust OSC Clock Frequency                                   | 84   |

| Table 6-7 PLL Clock State Register (PLLLCK, SFR 0xA3)                                | 84   |

| Table 6-8 Register 1 to Adjust Clock Frequency of Specific Functional Blocks               | 85  |

|--------------------------------------------------------------------------------------------|-----|

| Table 6-9 Register 2 to Adjust Clock Frequency of Specific Functional Blocks               | 86  |

| Table 6-10 OSC Clock State Register                                                        | 86  |

| Table 7-1 Factors Affecting Power Consumption of Each Unit                                 | 87  |

| Table 7-2 OSC State of System                                                              | 88  |

| Table 7-3 Power Consumption When System Working at Full Speed                              | 89  |

| Table 7-4 Configuration for Sleeping State                                                 | 93  |

| Table 7-5 Power Consumption in Sleeping State                                              | 94  |

| Table 7-6 Register for Clock Control                                                       | 95  |

| Table 7-7 Register to Indicate Power Supply State                                          | 96  |

| Table 9-1 Registers Related to Comparator CB                                               | 101 |

| Table 10-1 Buffer Registers and Data to Be Written or Read                                 | 104 |

| Table 10-2 Configuration of CLK2                                                           | 105 |

| Table 10-3 Analog PGA Gain Configuration for Current and Voltage Analog Input              | 108 |

| Table 10-4 Enable/Disable ADCs                                                             | 109 |

| Table 10-5 Control Bit for Switching Current Signals                                       | 110 |

| Table 10-6 f <sub>smpl</sub> Determines Phase Compensation Resolution and Correction Range | 112 |

| Table 10-7 Registers for Phase Compensation                                                | 112 |

| Table 10-8 Enable/Disable Digital Inputs                                                   | 112 |

| Table 10-9 DPGA Gain Selection for Digital Signals                                         | 113 |

| Table 10-10 Configuring for RMS Calculation and Calibration                                | 115 |

| Table 10-11 Functions of E2 Path                                                           | 116 |

| Table 10-12 Register Configuration for Energy Accumulation                                 | 119 |

| Table 10-13 Configurations for Energy Pulse Generation Rate and CF Pulse Output            | 120 |

| Table 10-14 Configure for No-Load Detection                                                | 122 |

| Table 10-15 Registers for Meter Calibration                                                | 127 |

| Table 11-1 Interrupt Sources                                                               | 133 |

| Table 11-2 IE (SFR 0xA8)                                                                   | 137 |

| Table 11-3 EIE (SFR 0xE8)                                                                  | 138 |

| Table 11-4 EXIF (SFR 0x91)                                                                 | 139 |

| Table 11-5 EICON (SFR 0xD8)                                                                | 139 |

| Table 11-6 IP (SFR 0xB8)                                                                   | 140 |

| Table 11-7 EIP (SFR 0xF8)                                                   | 140 |

|-----------------------------------------------------------------------------|-----|

| Table 11-8 Interrupt Events to Trigger Interrupt 8                          | 142 |

| Table 11-9 Extended Interrupt Flag (Request) Register (ExInt2IFG, 0x2840)   | 142 |

| Table 11-10 Extended Interrupt Input Type Register (ExInt2IN, 0x2841)       | 143 |

| Table 11-11 Extended Interrupt Output Type Register (ExInt2OUT, 0x2842)     | 143 |

| Table 11-12 Extended Interrupt Enable Register (ExInt2IE, 0x2843)           | 143 |

| Table 11-13 Extended Interrupt Pending Register (ExInt2OV, 0x2844)          | 143 |

| Table 11-14 Interrupt Event to Trigger Interrupt 9                          | 144 |

| Table 11-15 Extended Interrupt Flag (Request) Register (ExInt3IFG, 0x2848)  | 144 |

| Table 11-16 Extended Interrupt Input Type Register (ExInt3IN, 0x2849)       | 145 |

| Table 11-17 Extended Interrupt Output Type Register (ExInt3OUT, 0x284A)     | 145 |

| Table 11-18 Extended Interrupt Enable Register (ExInt3IE, 0x284B)           | 145 |

| Table 11-19 Extended Interrupt Pending Register (ExInt3OV, 0x284C)          | 145 |

| Table 11-20 Interrupt Events to Trigger Interrupt 10                        | 146 |

| Table 11-21 Extended Interrupt Flag (Request) Register (ExInt4IFG, 0x2850)  | 146 |

| Table 11-22 Extended Interrupt Input Type Register (ExInt4IN, 0x2851)       | 147 |

| Table 11-23 Extended Interrupt Output Type Register (ExInt4OUT, 0x2852)     | 147 |

| Table 11-24 Extended Interrupt Enable Register (ExInt4IE, 0x2853)           | 147 |

| Table 11-25 Extended Interrupt Pending Register (ExInt4OV, 0x2854)          | 147 |

| Table 11-26 Interrupt Events to Trigger Interrupt 11                        | 148 |

| Table 11-27 Extended Interrupt Flag (Request) Register (ExInt5IFG, 0x28A2)  | 148 |

| Table 11-28 Extended Interrupt Input Type Register (ExInt5IN, 0x28A3)       | 148 |

| Table 11-29 Extended Interrupt Output Type Register (ExInt5OUT, 0x28A4)     | 148 |

| Table 11-30 Extended Interrupt Enable Register (ExInt5IE, 0x28A5)           | 149 |

| Table 11-31 Extended Interrupt Pending Register (ExInt5OV, 0x28A6)          | 149 |

| Table 12-1 TimerA-Related Registers                                         | 151 |

| Table 12-2 Timer A Counter/Timer Register (TAR, 0x2902~0x2903)              | 152 |

| Table 12-3 Timer A Control Register (TACTL, 0x2900)                         | 152 |

| Table 12-4 Timer A Compare/Capture Control Registers (0x2904~0x2909)        | 155 |

| Table 12-5 Bit Description of CKCON (SFR 0x8E)                              | 161 |

| Table 12-6 Timer0/1 Mode Control Special Function Register (TMOD, SFR 0x89) | 162 |

| Table 12-7 Timer0/1 Control Special Function Register (TCON, SFR 0x88)      | 163 |

| Table 12-8 Timer2 Control Special Function Register (T2CON, SFR 0xC8)              | 167 |

|------------------------------------------------------------------------------------|-----|

| Table 12-9 Timer 2 Mode                                                            | 168 |

| Table 12-10 UART1 Control Special Function Register (SCON1, SFR 0xC0)              | 171 |

| Table 12-11 Extended UART Serial Interfaces Registers                              | 172 |

| Table 12-12 UARTx Control/Status Register (TCON2/TCON3/TCON4/TCON5)                | 173 |

| Table 12-13 UARTx Timers Mode Control Register (TMOD2/TMOD3/TMOD4/TMOD5)           | 174 |

| Table 12-14 UARTx Control Register (SCON2/SCON3/SCON4/SCON5)                       | 175 |

| Table 12-15 UARTx Buffer Register (SBUF2/SBUF3/SBUF4/SBUF5)                        | 176 |

| Table 12-16 TXD2 Type Register (Txd2FS, 0x28CF)                                    | 176 |

| Table 12-17 Carrier Wave Generation Registers                                      | 177 |

| Table 12-18 UART Modes                                                             | 177 |

| Table 12-19 EUART Baud Rate Generators                                             | 181 |

| Table 12-20 EUART Buffer Register (DATAA/DATAB, 0x2A03/0x2B03)                     | 181 |

| Table 12-21 EUART Information Register (INFOA/INFOB, 0x2A04/0x2B04)                | 181 |

| Table 12-22 EUART Configuration Register (CFGA/CFGB, 0x2A05/0x2B05)                | 182 |

| Table 12-23 Pulse Width Modulation Clock Generators                                | 187 |

| Table 13-1 Description of Different Frame Structures                               | 189 |

| Table 13-2 Register to Disable or Enable GPSI                                      | 192 |

| Table 13-3 GPSI Control Register (SICFG, 0x2F01)                                   | 192 |

| Table 13-4 GPSI Timer Divider Registers (SITHH/SITHL, 0x2F03/0x2F02)               | 193 |

| Table 13-5 GPSI Data Register (SIDAT, 0x2F04)                                      | 193 |

| Table 13-6 GPSI Communication Flag Register (SIFLG, 0x2F05)                        | 193 |

| Table 14-1 VLCD to Configuration of [LDO3SEL<2:0>] and [VLCD]                      | 196 |

| Table 14-2 RAM Byte Allocation for Segments of LCD Panel of 1/4 Duty               | 197 |

| Table 14-3 RAM Byte Allocation for Segments of LCD Panel of 1/6Duty When 6COMTYPE= | =0  |

|                                                                                    |     |

| Table 14-4 RAM Byte Allocation for Segments of LCD Panel of 1/6 Duty When 6COMTYPE |     |

| Table 14-5 RAM Byte Allocation for Segments of LCD Panel of 1/8 Duty               | 200 |

| Table 14-6 LCD Control Register (LCDCtrl, 0x2C1E)                                  | 206 |

| Table 14-7 Enable/Disable CLK3                                                     |     |

| Table 14-8 Register to Select Bias Mode                                            |     |

| Table 14-9 LCD Waveform Voltage Configuration 1                                    |     |

| -                                                                                  |     |

| Table 14-10 LCD Waveform Voltage Configuration 2                        | 208 |

|-------------------------------------------------------------------------|-----|

| Table 14-11 SEG Control Registers (R/W)                                 | 209 |

| Table 15-1 P0 Output Enable Register (P0OE, 0x28A8)                     | 211 |

| Table 15-2 P0 Input Enable Register (P0IE, 0x28A9)                      | 211 |

| Table 15-3 P0 Output Data Register (P0OD, 0x28AA)                       | 211 |

| Table 15-4 P0 Input Data Register (P0ID, 0x28AB)                        | 211 |

| Table 15-5 P1 Output Enable Register (P1OE, 0x28AC)                     | 212 |

| Table 15-6 P1 Input Enable Register (P1IE, 0x28AD)                      | 213 |

| Table 15-7 P1 Output Data Register (P1OD, 0x28AE)                       | 213 |

| Table 15-8 P1 Input Data Register (P1ID, 0x28AF)                        | 213 |

| Table 15-9 P1.0 Special Function Register (P10FS, 0x28C4, R/W)          | 213 |

| Table 15-10 P1.1 Special Function Register (P11FS, 0x28C5, R/W)         | 213 |

| Table 15-11 P1.2 Special Function Register (P12FS, 0x28C6, R/W)         | 214 |

| Table 15-12 P1.3 Special Function Register (P13FS, 0x28C7, R/W)         | 214 |

| Table 15-13 P1.4 Special Function Register (P14FS, 0x28C8)              | 214 |

| Table 15-14 P2 Output Enable Register (P2OE, 0x28B0)                    | 215 |

| Table 15-15 P2 Input Enable Register (P2IE, 0x28B1)                     | 215 |

| Table 15-16 P2 Output Data Register (P2OD, 0x28B2)                      | 216 |

| Table 15-17 P2 Input Data Register (P2ID, 0x28B3)                       | 216 |

| Table 15-18 P2.0 Special Function Register (P20FS, 0x28C9, R/W)         | 216 |

| Table 15-19 P2.1 Special Function Register (P21FS, 0x28CA, R/W)         | 216 |

| Table 15-20 P2.2 Special Function Register (P22FS, 0x28CB, R/W) (V98XX) | 217 |

| Table 15-21 P2.3 Special Function Register (P23FS, 0x28CC, R/W) (V98XX) | 217 |

| Table 15-22 P2.4 Special Function Register (P24FS, 0x28CD, R/W)         | 217 |

| Table 15-23 P2.5 Special Function Register (P25FS, 0x28CE, R/W)         | 217 |

| Table 15-24 P3 Output Enable Register (P3OE, 0x28B4)                    | 218 |

| Table 15-25 P3 Input Enable Register (P3IE, 0x28B5)                     | 218 |

| Table 15-26 P3 Output Data Register (P3OD, 0x28B6)                      | 218 |

| Table 15-27 P3 Input Data Register (P3ID, 0x28B7)                       | 218 |

| Table 15-28 P4 Output Enable Register (P4OE, 0x28B8)                    | 219 |

| Table 15-29 P4 Input Enable Register (P4IE, 0x28B9)                     | 220 |

| Table 15-30 P4 Output Data Register (P4OD, 0x28BA)                      | 220 |

| Table 15-31 P4 Input Data Register (P4ID, 0x28BB)                                 | . 220 |

|-----------------------------------------------------------------------------------|-------|

| Table 15-32 P5 Output Enable Register (P5OE, 0x28BC)                              | . 221 |

| Table 15-33 P5 Input Enable Register (P5IE, 0x28BD)                               | . 221 |

| Table 15-34 P5 Output Data Register (P5OD, 0x28BE)                                | 221   |

| Table 15-35 P5 Input Data Register (P5ID, 0x28BF)                                 | 221   |

| Table 15-36 P6 Output Enable Register (P6OE, 0x28C0)                              | 222   |

| Table 15-37 P6 Input Enable Register (P6IE, 0x28C1)                               | . 223 |

| Table 15-38 P6 Output Data Register (P6OD, 0x28C2)                                | . 223 |

| Table 15-39 P6 Input Data Register (P6ID, 0x28C3)                                 | . 223 |

| Table 15-40 P7 Output Enable Register (P7OE, 0x28D5)                              | 224   |

| Table 15-41 P7 Input Enable Register (P7IE, 0x28D6)                               | . 224 |

| Table 15-42 P7 Output Data Register (P7OD, 0x28D7)                                | . 224 |

| Table 15-43 P7 Input Data Register (P7ID, 0x28D8)                                 | . 225 |

| Table 15-44 P8 Output Enable Register (P8OE, 0x28D9)                              | . 225 |

| Table 15-45 P8 Input Enable Register (P8IE, 0x28DA)                               | . 226 |

| Table 15-46 P8 Output Data Register (P8OD, 0x28DB)                                | . 226 |

| Table 15-47 P8 Input Data Register (P8ID, 0x28DC)                                 | 226   |

| Table 15-48 P9 Output Enable Register (P9OE, SFR 0xA4)                            | 227   |

| Table 15-49 P9 Input Enable Register (P9IE, SFR 0xA5)                             | 227   |

| Table 15-50 P9 Output Data Register (P9OD, SFR 0xA6)                              | . 228 |

| Table 15-51 P9 Input Data Register (P9ID, SFR 0xA7)                               | . 228 |

| Table 15-52 P9 Special Function Register (P9FS, SFR 0xAD)                         | . 228 |

| Table 15-53 P10 Output Enable Register (P100E, SFR 0xA9)                          | . 230 |

| Table 15-54 P10 Input Enable Register (P10IE, SFR 0xAA)                           | . 230 |

| Table 15-55 P10 Output Data Register (P10OD, SFR 0xAB)                            | . 230 |

| Table 15-56 P10 Input Data Register (P10ID, SFR 0xAC)                             | . 230 |

| Table 15-57 Configuration for EUART Communication                                 | . 231 |

| Table 16-1 Enable/Disable CLK4                                                    | . 233 |

| Table 17-1 RTC Password Enable Register (RTCPEN, SFR 0x90)                        | . 240 |

| Table 17-2 RTC Password Register (RTCPWD, SFR 0x97)                               | . 240 |

| Table 17-3 RTC Wakeup Interval Register (INTRTC, SFR 0x96)                        | . 240 |

| Table 17-4 RTC Seconds Wake-up Interval Configuration Register (SECINT, SFR 0xDF) | 241   |

| Table 17-5 Flag Bit of RTC Wakeup Event                                          | 241 |

|----------------------------------------------------------------------------------|-----|

| Table 17-6 RTC Calibration Registers (RTCCH/RTCCL, SFR 0x94/0x95)                | 241 |

| Table 17-7 RTC Data Reading Enable Register (RDRTC, SFR 0xDA)                    | 241 |

| Table 17-8 PLL Clock Divider Registers (DIVTHH/DIVTHM/DIVTHL, SFR 0xDB/0xDC/0xDD | -   |

| Table 17-9 PLL Counter State Register (PLLCNTST, SFR 0xDE)                       | 242 |

| Table 17-10 RTC Timing Registers                                                 | 242 |

| Table 18-1 ADC Control Register 0 (CtrlADC0, 0x2858)                             |     |

| Table 18-2 ADC Control Register 1 (CtrlADC1, 0x2859)                             | 244 |

| Table 18-3 ADC Control Register 2 (CtrlADC2, 0x285A)                             | 245 |

| Table 18-4 ADC Control Register 3 (CtrlADC3, 0x285B)                             | 245 |

| Table 18-5 Battery Discharge Control Register (CtrlBAT, 0x285C)                  | 246 |

| Table 18-6 ADC Control Register 4 (CtrlADC4, 0x285D)                             | 246 |

| Table 18-7 LCD Driver Voltage Control Register (CtrlLCDV, 0x285E)                | 246 |

| Table 18-8 Crystal Control Register 1 (CtrlCry1, 0x2860)                         | 247 |

| Table 18-9 Crystal Control Register 2 (CtrlCry2, 0x2861)                         | 247 |

| Table 18-10 BandGap Control Register (CtrlBGP, 0x2862)                           | 247 |

| Table 18-11 ADC Control Register 5 (CtrlADC5, 0x2863)                            | 248 |

| Table 18-12 ADC Control Register 6 (CtrlADC6, 0x2864)                            | 249 |

| Table 18-13 Channel M Control Register (CtrlM, 0x2865)                           | 249 |

| Table 18-14 LDO Control Register (CtrlLDO, 0x2866)                               |     |

| Table 18-15 Clock Control Register (CtrlCLK, 0x2867)                             | 250 |

| Table 18-16 PLL Control Register (CtrlPLL, 0x2868)                               | 250 |

| Table 18-17 Analog Circuits State Register (ANState, 0x286B)                     | 251 |

| Table 18-18 PM Control Register 1 (PMCtrl1, 0x2878)                              | 251 |

| Table 18-19 PM Control Register 2 (PMCtrl2, 0x2879)                              | 252 |

| Table 18-20 PM Control Register 3 (PMCtrl3, 0x287A)                              | 252 |

| Table 18-21 Phase Compensation Control Register 1 (PHCCtrl1, 0x287B)             | 253 |

| Table 18-22 Phase Compensation Control Register 2 (PHCCtrl2, 0x287C)             | 254 |

| Table 18-23 PM Control Register 4 (PMCtrl4, 0x287D)                              | 254 |

| Table 18-24 CF Pulse Output Control Register (CFCtrl, 0x287E)                    | 254 |

| Table 18-25 No-Load Detection Indication Register (CRPST, 0x287F)                | 255 |

| Table 18-26 Current Detection Control Register (IDET, 0x2886)                    | 256 |

| Table 18-27 Signal Waveform Registers (R/W)                              | 257 |

|--------------------------------------------------------------------------|-----|

| Table 18-28 Power and RMS Registers (R/W)                                | 257 |

| Table 18-29 Energy Accumulators and Energy Pulse Counters (R/W)          | 258 |

| Table 18-30 Line Frequency Register (DATAFREQ, 0x10FD)                   | 259 |

| Table 18-31 Data Registers for Channel M                                 | 259 |

| Table 18-32 Registers for Gain Calibration (R/W)                         | 259 |

| Table 18-33 Registers for Power Offset Calibration (R/W)                 | 260 |

| Table 18-34 Band-pass Filter Coefficient Register (0x10EF, R/W)          | 260 |

| Table 18-35 Energy Threshold Registers and Constant Power Register (R/W) | 260 |

| Table 18-36 Threshold Register for Current Detection (R/W)               | 261 |

# **1.Electrical Characteristics**

### 1.1. Absolute Maximum Ratings

Operating circumstance exceeding **"Absolute Maximum Ratings"** may cause the permanent damage to the device.

#### Table 1-1 Absolut Maximum Ratings

| Parameter                          | Min. | Max. | Unit | Description         |

|------------------------------------|------|------|------|---------------------|

| Analog Power Supply                | -0.3 | +8.0 | V    | Relative to ground. |

| Analog Current Input               | -0.3 | +5.0 | V    | Relative to ground. |

| Analog Voltage Input               | -0.3 | +5.0 | V    | Relative to ground. |

| Operating Temperature              | -40  | +85  | °C   |                     |

| Storage Temperature                | -40  | +125 | °C   | 1                   |

| Junction Temperature               | -    | 150  | °C   |                     |

| Lead Temperature (Soldering, 10 s) | -    | 300  | °C   |                     |

### 1.2. Energy Metering Specifications

All typical specifications are at TA = 25 °C, VDD5 = 5.0 V  $\pm 10\%$ , and  $f_{MTCLK}$  = 3.2768 MHz, unless otherwise noted.

#### Table 1-2 Energy Metering Specifications

| Parameter                    | Typ   | Unit   | Description                  |

|------------------------------|-------|--------|------------------------------|

| raiametei                    | Тур.  | Unit   | Description                  |

| Phase Error Between Channels |       |        |                              |

| PF=0.8 Capacitive            | ±0.05 | Degree | 37° phase lead in current    |

| PF=0.5 Inductive             | ±0.05 | Degree | 60° phase lag in current     |

| Active Energy Metering       |       |        | -                            |

| Error                        | 0.1   | %      | Dynamic range of 5000:1@25°C |

| Bandwidth                    | 1.6   | kHz    |                              |

| Reactive Energy Metering     |       |        |                              |

| Error                        | 0.1   | %      | Dynamic range of 3000:1@25°C |

| Bandwidth                    | 1.6   | kHz    |                              |

| Apparent Power Metering      |       |        |                              |

| Parameter                        | Тур. | Unit   | Description                           |

|----------------------------------|------|--------|---------------------------------------|

| Error                            | 0.5  | %      | Dynamic range of 1000:1@25°C          |

| Voltage/Current RMS Metering     |      |        |                                       |

| Error                            | 0.5  | %      | Dynamic range of 1000:1@25°C          |

| Bandwidth                        | 1.6  | kHz    |                                       |

| CF Pulse Output                  |      |        |                                       |

| Maximum Output Frequency         | 6.4  | kHz    |                                       |

| Duty Cycle                       | 50%  |        | When active high pulse width < 80 ms. |

| Active High Pulse Width          | 80   | ms     | Configurable                          |

| Frequency Measurement Resolution | 0.05 | Hz/lsb | Measurement range: 35 Hz ~ 75 Hz      |

| Temperature Measurement Error    | ±1   | °C     | Measurement range: -40 °C ~ +85 °C    |

### **1.3. Analog Specifications**

All maximum and minimum specifications apply over the entire recommended operation range (T = -40 °C ~ +85 °C, VDD5 = 3.3 V or 5.0 V), unless otherwise noted. All typical specifications are at TA = 25 °C and VDD5 = 5.0 V  $\pm$ 10%, unless otherwise noted.

#### **Table 1-3 Analog Specifications**

| Parameter                            | Min. | Тур. | Max. | Unit | Description                                                                                  |

|--------------------------------------|------|------|------|------|----------------------------------------------------------------------------------------------|

|                                      | 3.6  | 5.0  | 5.5  | v    | 5 V powered                                                                                  |

| Analog Power Supply (VDD5)           | 2.5  | 3.3  | 3.6  | v    | 3.3 V powered                                                                                |

| LDO33 Output                         |      |      |      |      |                                                                                              |

| Voltage                              | 2.8  | 3.3  | 3.5  | v    | $V_{VDD5} \ge 4 V; I_{L33} = 16$<br>mA Programmable                                          |

| Load Current (IL33)                  |      |      | 30   | mA   | Current dissipated on<br>IOs should not be over<br>the maximum driving<br>capacity of LDO33. |

| Digital Power Supply                 |      |      |      |      |                                                                                              |

| Voltage                              | 1.3  | 1.8  | 2.0  | v    | Programmable                                                                                 |

| Load Current ( $I_{LD}$ )            |      |      | 35   | mA   |                                                                                              |

| POR/BOR Detection Threshold ("DVCC") |      | 1.4  |      | v    | Error: ±10%                                                                                  |

Power-Down Detection Threshold ("VDCIN")

|                                 | - i  | •      | 1            | Î.     |                              |  |  |  |

|---------------------------------|------|--------|--------------|--------|------------------------------|--|--|--|

| Parameter                       | Min. | Тур.   | Max.         | Unit   | Description                  |  |  |  |

| Maximum Signal Level            | 0    |        | VDD          | v      |                              |  |  |  |

| Input Impedance (DC)            |      | 1.5    |              | MΏ     |                              |  |  |  |

| Detection Threshold for "PWRDN" |      | 1.0    |              | v      |                              |  |  |  |

| Detection Threshold for "PWRUP" |      | 1.1    |              | v      |                              |  |  |  |

| Analog Inputs                   |      |        |              |        |                              |  |  |  |

| Maximum Signal Levels           | -200 |        | +200         | mV     | Peak value                   |  |  |  |

| ADC Performance                 |      |        |              |        |                              |  |  |  |

| DC Offset                       |      |        | 15           | mV     |                              |  |  |  |

| Effective Bits                  |      | 20     |              | BIT    | Sign bits are excluded.      |  |  |  |

| Bandwidth (-3dB)                |      | 1.6    |              | kHz    |                              |  |  |  |

| ADC Operating Current           |      |        |              |        |                              |  |  |  |

| Voltage Channel                 |      | 307    |              | μA     | )                            |  |  |  |

| Current Channel                 |      | 485    |              | μA     | f <sub>ADC</sub> = 819.2 kHz |  |  |  |

| Measurement Channel             |      | 238    |              | μA     |                              |  |  |  |

| On-Chip Crystal Oscillator      |      |        |              |        |                              |  |  |  |

| Crystal Frequency               |      | 32.768 |              | kHz    |                              |  |  |  |

| On-Chip Reference (BandGap)     |      |        |              |        |                              |  |  |  |

| Reference Error                 | -18  | $\sum$ | 18           | mV     |                              |  |  |  |

| Power Supply Rejection Ratio    |      | 80     |              | dB     |                              |  |  |  |

| Temperature Coefficient         |      | 10     | 30           | ppm/°C |                              |  |  |  |

| Output Voltage                  |      | 1.185  |              | v      |                              |  |  |  |

| Analog Comparator CB            |      |        |              |        |                              |  |  |  |

| Input Voltage                   | 0    |        | VDD5<br>-0.8 | v      |                              |  |  |  |

| Load Current                    |      | 186.2  |              | nA     | Bias current = 20 nA         |  |  |  |

| Delay Time                      | 2.7  | 3.0    | 4.0          | μs     | Square wave = 50 kHz         |  |  |  |

| Load Current                    |      | 664.6  |              | nA     | Bias current = 200 nA        |  |  |  |

| Delay Time                      | 0.20 | 0.37   | 0.60         | μs     | Square wave = 50 kHz         |  |  |  |

### **1.4. Digital Interface Specifications**

All maximum and minimum specifications apply over the entire recommended operation range (T = -40 °C  $\sim$  +85 °C, VDD5 = 3.3 V or 5.0 V), unless otherwise noted.

| Parameter                     | Min. | Тур. | Max. | Unit | Description                                                                      |  |  |  |  |

|-------------------------------|------|------|------|------|----------------------------------------------------------------------------------|--|--|--|--|

| Digital IO, Output            |      |      |      |      |                                                                                  |  |  |  |  |

| Output High Voltage, Vон      | 2.4  |      |      | v    |                                                                                  |  |  |  |  |

| Isource                       |      | 10   | 12   | mA   | 12-mA current cannot damage the chip<br>in a short period of time; Long duration |  |  |  |  |

| Output Low Voltage, $V_{OL}$  |      |      | 0.4  | v    | of 10-mA or above current may cause                                              |  |  |  |  |

| Isink                         |      | 10   | 12   | mA   | damage to the chip.                                                              |  |  |  |  |

| Digital IO, Input             |      |      |      |      |                                                                                  |  |  |  |  |

| Input High Voltage, $V_{INH}$ | 2.0  |      |      | v    |                                                                                  |  |  |  |  |

| Input Low Voltage, $V_{INL}$  |      |      | 0.8  | v    |                                                                                  |  |  |  |  |

#### **Table 1-4 Digital Interface Specifications**

### 1.5. Memory Specifications

All maximum and minimum specifications apply over the entire recommended operation range (T = -40 °C ~ +85 °C, VDD5 = 3.3 V or 5.0 V), unless otherwise noted. All typical specifications are at TA = 25 °C, VDD5 = 5.0 V  $\pm 10\%$  or f<sub>MCU</sub> = 13.1072 MHz, unless otherwise noted.

#### **Table 1-5 Memory Specifications**

| Parameter                   | Min.  | Тур. | Max. | Unit  | Description            |

|-----------------------------|-------|------|------|-------|------------------------|

| Flash Memory                |       |      |      |       |                        |

| Read Pulse Width            |       | 76   |      | ns    |                        |

| Endurance                   | 20000 |      |      | cycle | -40 °C ~ +85 °C        |

| Data Retention              | 100   |      |      | year  | 25°C                   |

| Data Retention              | 10    |      |      | year  | 85°C                   |

| Write Time, per byte        |       | 40   |      | μs    |                        |

| Page Erase Time (512 bytes) |       | 40   |      | ms    |                        |

| Mass Erase Time             |       | 40   |      | ms    |                        |

| RAM                         |       |      |      |       |                        |

| Data Retention Voltage      | 1.62  |      |      | v     | DVCC output<br>voltage |

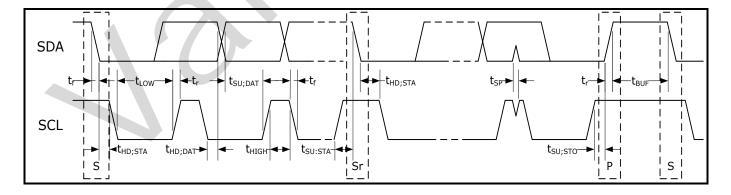

### **1.6. GPSI Timing Specifications**

All maximum and minimum specifications apply over the entire recommended operation range (T = -40 °C ~ +85 °C, VDD5 = 3.3 V or 5.0 V  $\pm$ 10%), unless otherwise noted.

| Parame              | ter                                                                 | Min.  | Max. | Unit |

|---------------------|---------------------------------------------------------------------|-------|------|------|

| fscl                | SCL frequency                                                       |       | 400  | kHz  |

| <b>t</b> hd;sta     | START condition hold time (Then, the first SCL pulse is generated.) | 1.875 |      | μs   |

| t <sub>LOW</sub>    | SCL low pulse width                                                 | 1.25  |      | μs   |

| tніgн               | SCL high pulse width                                                | 1.25  |      | μs   |

| <b>t</b> su;sta     | RESTART condition setup time                                        | 0.625 |      | μs   |

| <b>t</b> hd;dat     | Data hold time                                                      | 0.625 |      | μs   |

| t <sub>su;dat</sub> | Data setup time                                                     | 0.625 |      | μs   |

| tr                  | Rising time of both SDA and SCL                                     |       | 50   | ns   |

| t <sub>f</sub>      | Falling time of both SDA and SCL                                    |       | 50   | ns   |

| <b>t</b> su;sто     | STOP condition setup time                                           | 0.625 |      | μs   |

| tbur                | Bus free time between STOP condition and START condition            |       | N/A  |      |

| t <sub>SP</sub>     | Pulse width of spike suppressed                                     |       | N/A  |      |

#### Table 1-6 GPSI Timing Specifications

### **1.7. Typical Operating Current**

**Table 1-7 Typical Operating Current**

| Mode               | Тур. | Unit | Description                                                                                                                                                                                                                 |

|--------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|